- Joined

- May 30, 2021

- Messages

- 9

- Motherboard

- Gigabyte H97-HD3

- CPU

- i5 > Need full CPU name > See Forum Rules!

- Graphics

- RX 580

No. You are not able to replicate this using an SSDT. I can give you technical reasons if you'd like but it might be boring.

I can see why you might think so, because we do create an embedded controller with SSDT-EC.aml etc. The difference is with EHCI and XHCI we are rerouting already existing controllers.

Basically there are very specific use cases for FakePCIID_XHCIMux.kext.

Remember you also need FakePCIID.kext to create and attach the new device you are going to spoof.

What is the "quirk" with 7/8/9 chipsets you are referring to?

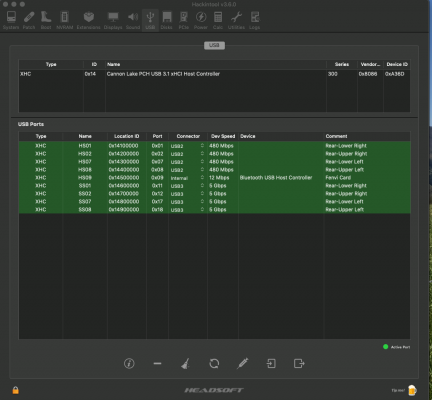

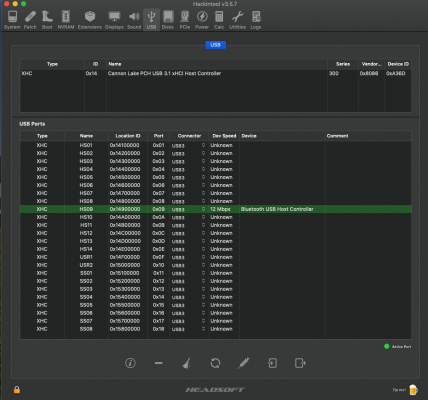

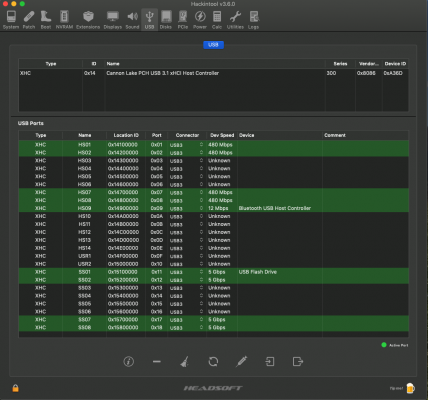

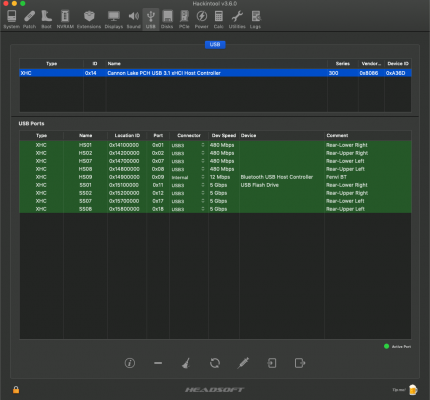

Just use Hackintool as per the guide and maybe read the older one which does cover mixed controller setups etc.

From RehabMan's GitHub:

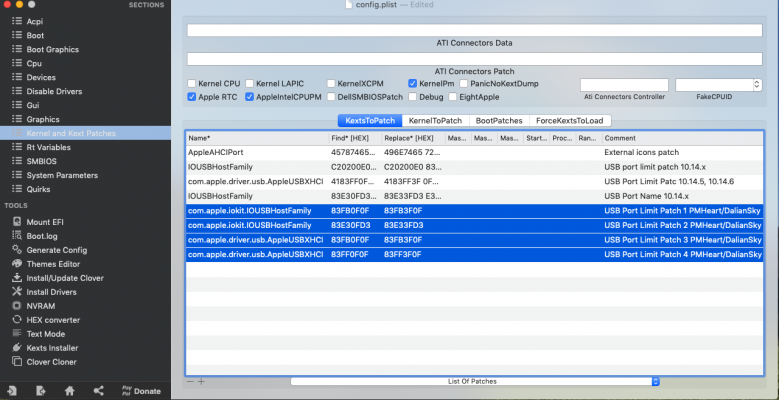

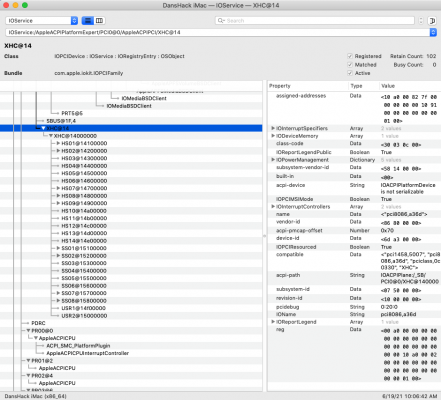

FakePCIID_XHCIMux.kext This kext will attach to 8086:1e31, 8086:9c31, 8086:9cb1, 8086:9c31, and 8086:8cb1 This injector is a bit of an extension to normal FakePCIID duties. It doesn't actually fake any PCI IDs. Rather, it forces certain values to XUSB2PR (PCI config offset 0xD0) on the Intel XHCI USB3 controller. The effect is to route any USB2 devices attached to the USB2 pins on the XHC ports to EHC1. In other words, handle USB2 devices with the USB2 drivers instead of the USB3 drivers (AppleUSBEHCI vs. AppleUSBXHCI).

So normally what is a complex "multiplex" DSDT patch (that is not well understood), is a simple kext install.

Configuration properties and their defaults: RM,pr2-force <00 00 00 00>. By default forces all XHCI ports to route USB2 devices to EHC1. RM,pr2-init <01>. Will write RM,pr2-force value at startup if non-zero. RM,pr2-block <01>. Will block writes to XUSB2PR if non-zero. RM,pr2m-block <01>. No evidence that OS X drivers attempt to write XUSB2PRM (offset 0xD4), but since this kext relies on a valid value here (as provided by the BIOS), writes to it are blocked if non-zero. RM,pr2-honor-pr2m <01>: Changes to XUSB2PR will be masked by XUSB2PRM if this is non-zero. RM,pr2-chipset-mask: Writes to XUSB2PR are masked by this value. This is defined by the chipset documentation. Default value depends on chipset.

Refer to Intel 7/8/9-series chipset data sheet for more info

-----------

Using this on my Z97, I have 17 (16 external, 1 internal wifi/BT) USB ports working. 6 USB 3.0 which is a total of 12 ports and 4 USB 2 ports.

Since he mentioned the 7/8/9 chipset in particular I presume this is something unique to those.