- Joined

- Jan 20, 2020

- Messages

- 53

- Motherboard

- Gigabyte Z390 Designare

- CPU

- i9 9900k

- Graphics

- RX580

- Mac

- Mobile Phone

Just follow the steps in the mini guide HERE

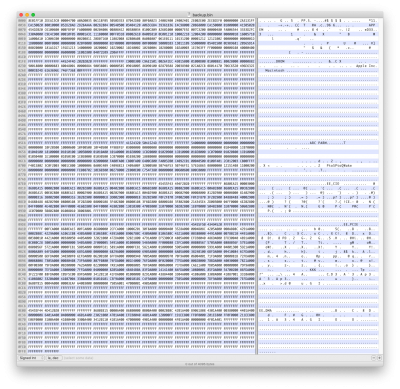

I’ve seen this guide, it’s just that I’m on OpenCore and not Clover. It also appears that I have working NVRAM. (Did the [TestVar Hello] on the bottom of the guide). Could some other issue be the cause of FaceTime/Message not working?

My original Question Post: Here

Last edited: