- Joined

- Jan 1, 2020

- Messages

- 616

- Motherboard

- MSI Z490 MPG Gaming Edge Wifi

- CPU

- i5-10600K

- Graphics

- RX 6600 XT

- Mac

Have already tested by changing RH10, RH14 and others for system reset data.. all resulting on Thunderbolt Local Node and ThunderboltPort tree disappears.Do you mean:

- Create a PINI() method in the old (standard) Thunderbolt SSDT and add SHOW() into it?

- If so, yes no problem at all. Can do this in the evening.

- But if you would like to see the PINI() method I used in the TbtOnPch() function for the hot-plug photographs, that function looks like this:

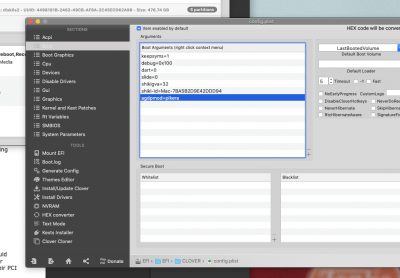

Code:Method (PINI, 0, NotSerialized) // _INI: Initialize { If (OSDW ()) { DBG1 ("RP05 Initialize") Acquire (TCFG, 0xFFFF) R018 = R_18 // RP Pri Bus R019 = R_19 // RP Sec Bus R01A = R_1A // RP Sub Bus R01C = R_1C // RP IO base/limit from UEFI R020 = R_20 // RP base/limit from UEFI R024 = R_24 // RP prefetch base/limit from UEFI R028 = R_28 R02C = R_2C R118 = R_19 // UPSB Pri Bus = RP Sec Bus (UEFI) R119 = (R_19 + One) // UPSB Sec Bus = RP Sec Bus + 1 R11A = R_1A // UPSB Sub Bus = RP Sub Bus (UEFI) R11C = R01C // UPSB IO base/limit = RP IO base/limit (UEFI) R120 = R020 // UPSB mem base/limit = RP mem base/limit (UEFI) R124 = R024 // UPSB pre base/limit = RP pre base/limit (UEFI) R128 = R028 R12C = R02C R218 = R119 // DSB0 Pri Bus = UPSB Sec Bus R219 = (R119 + One) // DSB0 Sec Bus = UPSB Sec Bus + 1 R21A = (R119 + One) // DSB0 Sub Bus = UPSB Sub Bus R21C = R01C // DSB0 IO base/limit = UPSB IO base/limit R220 = 0x82008200 // DSB0 mem base/limit = UPSB mem base/limit (from REGISTERS) // R220 = R120 // DSB0 mem base/limit = UPSB mem base/limit R224 = 0x1fff1 // DSB0 pre base/limit = UPSB pre base/limit R228 = Zero R22C = Zero R318 = R119 // DSB1 Pri Bus = UPSB Sec Bus R319 = (R119 + 0x02) // DSB1 Sec Bus = UPSB Sec Bus + 2 R31A = (R119 + 0x02) // DSB1 Sub Bus = no children R31C = Zero // DSB1 disable IO R320 = Zero // DSB1 disable mem R324 = Zero // DSB1 disable prefetch R328 = Zero R32C = Zero R418 = R119 // DSB2 Pri Bus = UPSB Sec Bus R419 = (((R_1A - R219) >> One) + R219) // DSB2 Sec Bus = UPSB Sec Bus + 3 R41A = (((R_1A - R219) >> One) + R219) // DSB2 Sub Bus = no children R41C = 0x1f1 // DSB2 disable IO R420 = 0x6bf06bf0 // DSB2 disable mem R424 = 0x1fff1 // DSB2 disable prefetch R428 = Zero R42C = Zero RVES = 0x130004 // DSB2 offset 0x564, unknown R518 = R119 // DSB4 Pri Bus = UPSB Sec Bus R519 = 0x3d // DSB4 Sec Bus = UPSB Sec Bus + 4 R51A = 0x70 // DSB4 Sub Bus = no children R51C = 0x1f1 // DSB4 disable IO R520 = 0x81f06c00 // DSB4 disable mem R524 = 0x49f12001 // DSB4 disable prefetch R528 = 0x60 R52C = 0x60 // RH10 = (R220 & 0xFFFC) << 16 // NHI0 BAR0 = DSB0 mem base RH10 = ((R220 & 0xFFF00000)) // NHI0 BAR0 = DSB0 mem base (from REGISTERS) // RH14 = Zero // NHI0 BAR1 unused RH14 = ((RH10 + 0x00040000)) // NHI0 BAR1 unused (from REGISTERS) Sleep (One) ICMB (Zero) Release (TCFG) } }