Hi there. Thanks so much for the guide. The port limit patch and XCH renames weren't enough to get USB3 working on my board, I had to use all of your patches mentioned to even get testing working.

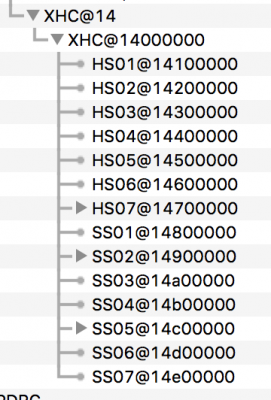

I followed your guide very closely to map out my ports. I am confused, however, on the reported mapping. The way that it looks like the ports are mapped on my board are completely insane. The first FOUR ports share one "port" and all the others have independent ports. Did I do something wrong or could this be correct?

Questions:

1. Does it make sense that one "port" could be controlling 4 USB ports and then one controller each for the remaining intel ports?

a. If it doesn't make sense, how can I trouble shoot this?

2. The GenericXCH USB got the ASMedia ports working for USB 3 (but not USB 2. obviously. but what kext do I use for USB 2?)

3. None of the templates match my device ID <31 8d 00 00> so do I just create a whole new entry for that?

4. For the sake of my sanity, would the syntax for the AML be something like:

Code:

"8086_318d", Package()

{

"port-count", Buffer() { 26, 0, 0, 0 },

"ports", Package()

{

"HS01", Package()

{

"UsbConnector", 3,

"port", Buffer() { 1, 0, 0, 0 },

},

"SSP1", Package()

{

"UsbConnector", 3,

"port", Buffer() { 2, 0, 0, 0 },

},

}

etc, etc?

I am confused what number to put inside the array. Does the array number match the physical port number or the logical one?

5. For my board, would SSP5 and HS09 have the same array numbers even though there are 4 physical ports?

6. Would SSP1 and HS01 have the same array numbers or different? Sorry I'm very not clear on syntax here.

7. I use *many* USB devices and hubs at any given moment. What do I have to do to make sure hubs work? This will change on a daily basis because of how many USB devices I'm connecting and disconnecting. I am extremely confused about what to do with external hubs and I don't know how to to map them or treat them in the aml.

8. Do I need to do anything to manage USB hubs connected via Thunderbolt or will they just work?

9. I wasn't clear on the usage of FakePCIID_XHCIMux.kext and FakePCIID kext. I installed these and the system would boot but not allow me any control of any USB device. I had a never ending spinwheel on boot and couldn't even log in, deleted the kexts. Do I need these orrrr... ?

I should mention that this board has zero USB2 ports except for in the internal headers.

Thanks so much for your time!