You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

pastrychef's Asus ROG Strix Z370-G Gaming (WI-FI AC) build w/ i9-9900K + AMD 6600 XT

- Thread starter pastrychef

- Start date

pastrychef

Moderator

- Joined

- May 29, 2013

- Messages

- 19,458

- Motherboard

- Mac Studio - Mac13,1

- CPU

- M1 Max

- Graphics

- 32 Core

- Mac

- Classic Mac

- Mobile Phone

Can you confirm that your Strix Z370 USB ports.aml is working, your XHC overrides look wrong ? those 8086_a12f overrides are for the 100 series boards. RehabMan has provided a template for 8086:a2af (200-series chipset XHC controller). Would that not be a better match? one other thing, it looks like you are over the port limitation if going by the guide that RehabMan wrote. Could you kindly explain.

One other reason I ask if it is working, I disassembled your USB ports.aml file:

Code:"UsbConnector", 3,

Code:"HS03", Package() // USB2 #1 from USB3 motherboard header, port <03 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x03, 0, 0, 0 }, }, "HS04", Package() // USB2 #2 from USB3 motherboard header, port <04 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x04, 0, 0, 0 }, }, "HS11", Package() // USB2 #1 on USB2 motherboard header 2, port <0b 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x0b, 0, 0, 0 }, }, "HS12", Package() // USB2 #2 on USB2 motherboard header 2, port<0c 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x0c, 0, 0, 0 }, }, "HS13", Package() // USB2 #1 on USB2 motherboard header 3, port <0d 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x0d, 0, 0, 0 }, }, "HS14", Package() // USB2 #2 on USB2 motherboard header 3 Internal Bluetooth, port<0e 00 00 00> { "UsbConnector", 255, "port", Buffer() { 0x0e, 0, 0, 0 }, }

You have internal USB initalised with value of 3, RehabMan say this should be set at 255 ?

Is it working ?

@RehabMan can you clarify please.

Yes, all my USB ports are in use except the USB 3.1 gen 2 ports. All are working.

From what I understand, 255 should be used for internal headers.

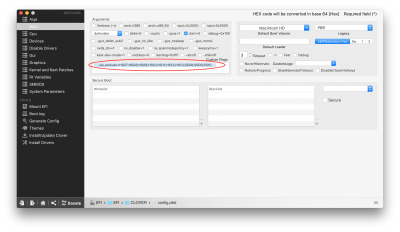

I followed the guide from here (see section 7.2). This method maps all ports then disables ports in config.plist to bring count down to 15 or less. I know of the alternate method to only map ports that will be used and doesn't require an entry in to config.plist, however, that is less friendly for sharing.

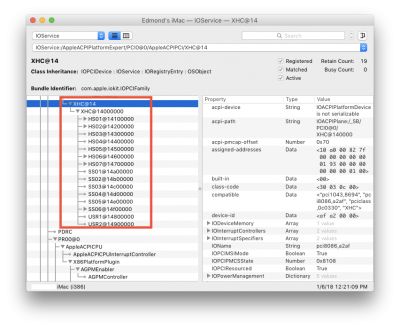

In IORegistryExplorer, you can see that I have 15 ports:

- Joined

- Jan 6, 2018

- Messages

- 7

- Motherboard

- ASUS ROG Strix Z370-F

- CPU

- i7-8700K

- Graphics

- GXT 1070 TI

Yes, all my USB ports are in use except the USB 3.1 gen 2 ports. All are working.

From what I understand, 255 should be used for internal headers.

I followed the guide from here (see section 7.2). This method maps all ports then disables ports in config.plist to bring count down to 15 or less. I know of the alternate method to only map ports that will be used and doesn't require an entry in to config.plist, however, that is less friendly for sharing.

View attachment 304079

In IORegistryExplorer, you can see that I have 15 ports:

View attachment 304080

You have the ports excluded using USBInjectAll and setting in config.plist to disable the ports. But, I am asking if you can confirm that Strix Z370 USB ports.aml is working on it's own with USBInjectAll.

Here below, is your Strix Z370 USB ports.aml file..

Code:

/*

* Intel ACPI Component Architecture

* AML Disassembler version 20140926-64 [Oct 24 2014]

* Copyright (c) 2000 - 2014 Intel Corporation

*

* Disassembly of iASLQOOC8z.aml, Sun Nov 22 09:50:28 2015

*

* Original Table Header:

* Signature "SSDT"

* Length 0x000002DA (730)

* Revision 0x01

* Checksum 0xCD

* OEM ID "sample"

* OEM Table ID "USBFix"

* OEM Revision 0x00003000 (12288)

* Compiler ID "INTL"

* Compiler Version 0x20140926 (538183974)

*/

DefinitionBlock ("SSDT-USB.aml", "SSDT", 1, "sample", "USBFix", 0x00003000)

{

// "USBInjectAllConfiguration" : override settings for USBInjectAll.kext

Device (UIAC)

{

Name (_HID, "UIA00000")

// "RehabManConFiguration"

Name (RMCF, Package ()

{

// XHC overrides for 100-series boards

"8086_a12f", Package()

{

"port-count", Buffer() { 0x18, 0, 0, 0}, // Highest port number is SS06 at 0x16

"ports", Package()

{ "HS01", Package() // USB2 under PS2 top, port <01 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x01, 0, 0, 0 },

},

"HS02", Package() // USB2 under PS2 bottom, port <02 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x02, 0, 0, 0 },

},

"HS03", Package() // USB2 #1 from USB3 motherboard header, port <03 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x03, 0, 0, 0 },

},

"HS04", Package() // USB2 #2 from USB3 motherboard header, port <04 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x04, 0, 0, 0 },

},

"HS05", Package() // USB2 under ethernet top, port <05 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x05, 0, 0, 0 },

},

"HS06", Package() // USB2 under ethernet bottom, port <06 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x06, 0, 0, 0 },

},

"HS07", Package() // USB2 to right of DisplayPort, port <07 00 00 00>

{

"UsbConnector", 255,

"port", Buffer() { 0x07, 0, 0, 0 },

},

"HS09", Package() // USB2 to right of HDMI, port <09 00 00 00>

{

"UsbConnector", 0,

"port", Buffer() { 0x08, 0, 0, 0 },

},

"HS10", Package() // USB2 to right of HDMI, port <0a 00 00 00>

{

"UsbConnector", 0,

"port", Buffer() { 0x08, 0, 0, 0 },

},

"HS11", Package() // USB2 #1 on USB2 motherboard header 2, port <0b 00 00 00>

{

"UsbConnector", 0,

"port", Buffer() { 0x0b, 0, 0, 0 },

},

"HS12", Package() // USB2 #2 on USB2 motherboard header 2, port<0c 00 00 00>

{

"UsbConnector", 0,

"port", Buffer() { 0x0c, 0, 0, 0 },

},

"HS13", Package() // USB2 #1 on USB2 motherboard header 3, port <0d 00 00 00>

{

"UsbConnector", 0,

"port", Buffer() { 0x0d, 0, 0, 0 },

},

"HS14", Package() // USB2 #2 on USB2 motherboard header 3 Internal Bluetooth, port<0e 00 00 00>

{

"UsbConnector", 255,

"port", Buffer() { 0x0e, 0, 0, 0 },

},

"SS01", Package() // USB3 under PS2 top, port <11 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x11, 0, 0, 0 },

},

"SS02", Package() // USB3 under PS2 bottom, port <12 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x12, 0, 0, 0 },

},

"SS03", Package() // USB3 from USB3 motherboard header, port <13 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x13, 0, 0, 0 },

},

"SS04", Package() // USB3 from USB3 motherboard header, port <14 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x14, 0, 0, 0 },

},

"SS05", Package() // USB3 below ethernet top, port <15 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x15, 0, 0, 0 },

},

"SS06", Package() // USB3 #2 below ethernet bottom, port <16 00 00 00>

{

"UsbConnector", 3,

"port", Buffer() { 0x16, 0, 0, 0 },

},

}

}

})

}

}As @RehabMan already said "No need to use uia_exclude for ports that are already excluded via the SSDT." Then Strix Z370 USB ports.aml file you are sharing is wrong ? it clearly has internal headers with value of 3 and 0 and not 255.

You can exclude ports with uia_exclude and USBInjectAll ( looking at your image this is what you are doing )

Strix Z370 USB ports.aml should work without uia_exclude. That Strix Z370 USB ports.aml file if working would inject more than 15 ports.

So yes, you have 15 port limit using USBInjectAll and uia_exclude.

But Strix Z370 USB ports.aml is doing nothing and you have your limit using USBInjectAll and uia_exclude.

If you remove the uia_exclude from config.plist you will see you are over the port limit.

Last edited:

pastrychef

Moderator

- Joined

- May 29, 2013

- Messages

- 19,458

- Motherboard

- Mac Studio - Mac13,1

- CPU

- M1 Max

- Graphics

- 32 Core

- Mac

- Classic Mac

- Mobile Phone

You have the ports excluded using USBInjectAll and setting in config.plist to disable the ports. But, I am asking if you can confirm that Strix Z370 USB ports.aml is working on it's own with USBInjectAll.

Yes, they can work on it's own without the ssdt-usb.aml but you would need the 15 port limit patch in KextsToPatch.

Here below, is your Strix Z370 USB ports.aml file..

Code:/* * Intel ACPI Component Architecture * AML Disassembler version 20140926-64 [Oct 24 2014] * Copyright (c) 2000 - 2014 Intel Corporation * * Disassembly of iASLQOOC8z.aml, Sun Nov 22 09:50:28 2015 * * Original Table Header: * Signature "SSDT" * Length 0x000002DA (730) * Revision 0x01 * Checksum 0xCD * OEM ID "sample" * OEM Table ID "USBFix" * OEM Revision 0x00003000 (12288) * Compiler ID "INTL" * Compiler Version 0x20140926 (538183974) */ DefinitionBlock ("SSDT-USB.aml", "SSDT", 1, "sample", "USBFix", 0x00003000) { // "USBInjectAllConfiguration" : override settings for USBInjectAll.kext Device (UIAC) { Name (_HID, "UIA00000") // "RehabManConFiguration" Name (RMCF, Package () { // XHC overrides for 100-series boards "8086_a12f", Package() { "port-count", Buffer() { 0x18, 0, 0, 0}, // Highest port number is SS06 at 0x16 "ports", Package() { "HS01", Package() // USB2 under PS2 top, port <01 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x01, 0, 0, 0 }, }, "HS02", Package() // USB2 under PS2 bottom, port <02 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x02, 0, 0, 0 }, }, "HS03", Package() // USB2 #1 from USB3 motherboard header, port <03 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x03, 0, 0, 0 }, }, "HS04", Package() // USB2 #2 from USB3 motherboard header, port <04 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x04, 0, 0, 0 }, }, "HS05", Package() // USB2 under ethernet top, port <05 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x05, 0, 0, 0 }, }, "HS06", Package() // USB2 under ethernet bottom, port <06 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x06, 0, 0, 0 }, }, "HS07", Package() // USB2 to right of DisplayPort, port <07 00 00 00> { "UsbConnector", 255, "port", Buffer() { 0x07, 0, 0, 0 }, }, "HS09", Package() // USB2 to right of HDMI, port <09 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x08, 0, 0, 0 }, }, "HS10", Package() // USB2 to right of HDMI, port <0a 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x08, 0, 0, 0 }, }, "HS11", Package() // USB2 #1 on USB2 motherboard header 2, port <0b 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x0b, 0, 0, 0 }, }, "HS12", Package() // USB2 #2 on USB2 motherboard header 2, port<0c 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x0c, 0, 0, 0 }, }, "HS13", Package() // USB2 #1 on USB2 motherboard header 3, port <0d 00 00 00> { "UsbConnector", 0, "port", Buffer() { 0x0d, 0, 0, 0 }, }, "HS14", Package() // USB2 #2 on USB2 motherboard header 3 Internal Bluetooth, port<0e 00 00 00> { "UsbConnector", 255, "port", Buffer() { 0x0e, 0, 0, 0 }, }, "SS01", Package() // USB3 under PS2 top, port <11 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x11, 0, 0, 0 }, }, "SS02", Package() // USB3 under PS2 bottom, port <12 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x12, 0, 0, 0 }, }, "SS03", Package() // USB3 from USB3 motherboard header, port <13 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x13, 0, 0, 0 }, }, "SS04", Package() // USB3 from USB3 motherboard header, port <14 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x14, 0, 0, 0 }, }, "SS05", Package() // USB3 below ethernet top, port <15 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x15, 0, 0, 0 }, }, "SS06", Package() // USB3 #2 below ethernet bottom, port <16 00 00 00> { "UsbConnector", 3, "port", Buffer() { 0x16, 0, 0, 0 }, }, } } }) } }

Yes, you are right. I should change HS11-HS13 to 255. But I assumed that everyone would disable those ports anyway. HS14 and HS7 are both 255 so that they will work with the Bluetooth part of Wi-Fi/Bluetooth cards.

HS03/SS03 and HS04/SS04 are using 0 and 3 because they are intended to be connected to external case ports, not internal use.

As @RehabMan already said "No need to use uia_exclude for ports that are already excluded via the SSDT." Then Strix Z370 USB ports.aml file you are sharing is wrong ? it clearly has internal headers with value of 3 and 0 and not 255.

You can exclude ports with uia_exclude and USBInjectAll ( looking at your image this is what you are doing )

Strix Z370 USB ports.aml should work without uia_exclude. That Strix Z370 USB ports.aml file if working would inject more than 15 ports.

Yes, like I said, that's another method. There are two ways to do this:

Method 1:

Only map ports that will be used and uia_exclude will not be needed.

Method 2:

Map all ports and use uia_exclude to exclude unused ports.

I chose method 2 because it is better for sharing with other users. If I used method one, HS14 would be disabled because I use HS07 for Bluetooth. That means that anyone who decides to use a Wi-Fi/Bluetooth card with a PCI-e adaptor will not have Bluetooth.

By choosing method 2, users can choose which ports to disable on their own.

So yes, you have 15 port limit using USBInjectAll and uia_exclude.

But Strix Z370 USB ports.aml is doing nothing and you have your limit using USBInjectAll and uia_exclude.

Yes, I will clarify that users need to use uia_exclude to bring their port numbers down.

- Joined

- Jan 6, 2018

- Messages

- 7

- Motherboard

- ASUS ROG Strix Z370-F

- CPU

- i7-8700K

- Graphics

- GXT 1070 TI

Remember, even with the use of the SSDT-USB.aml file, you still have use the uia_exclude custom flag (in Boot section of Clover Configurator) in your config.plist to bring the total port count to 13 or less (the last two ports are used by the two USB 3.1 gen 2 ports). Here's how mine looks:

No, as RehabMan said ::here::

No need to use uia_exclude for ports that are already excluded via the SSDT.

Good guide and writeup, despite the USB advise.

pastrychef

Moderator

- Joined

- May 29, 2013

- Messages

- 19,458

- Motherboard

- Mac Studio - Mac13,1

- CPU

- M1 Max

- Graphics

- 32 Core

- Mac

- Classic Mac

- Mobile Phone

Like I've said, I'm not using his method!!!!!!!!

You are not understanding what I'm saying.

There are different ways to reach the same result...

- Joined

- Jan 6, 2018

- Messages

- 7

- Motherboard

- ASUS ROG Strix Z370-F

- CPU

- i7-8700K

- Graphics

- GXT 1070 TI

I do understand!!!!!! and think your advise is wrong on this.

You have to be clear on this:

Some readers will assume your above quote is true. NO, uia_exclude custom flag is not required when using SSDT-USB.aml file period!

Method 1:

Only map ports that will be used and uia_exclude will not be needed.

Method 2:

Map all ports and use uia_exclude to exclude unused ports.

You have to be clear on this:

Remember, even with the use of the SSDT-USB.aml file, you still have use the uia_exclude custom flag

Some readers will assume your above quote is true. NO, uia_exclude custom flag is not required when using SSDT-USB.aml file period!

pastrychef

Moderator

- Joined

- May 29, 2013

- Messages

- 19,458

- Motherboard

- Mac Studio - Mac13,1

- CPU

- M1 Max

- Graphics

- 32 Core

- Mac

- Classic Mac

- Mobile Phone

Some readers will assume your above quote is true. NO, uia_exclude custom flag is not required when using SSDT-USB.aml file period!

It is if you use this method!!!!

- Joined

- Jan 6, 2018

- Messages

- 7

- Motherboard

- ASUS ROG Strix Z370-F

- CPU

- i7-8700K

- Graphics

- GXT 1070 TI

Can you then please explain this method 2 clearly in your guide !!!! Also your Strix Z370 USB ports.aml file needs updating, tbh it's messy and your overrides is wrong for a start.

Should be:

Most users on this forum, using Unibeast and Multibeast will expect to drop your Z370 USB ports.aml file into ACPI/patched and have sorted USB.

Code:

// XHC overrides for 100-series boards

"8086_a12f", Package()Should be:

Code:

// XHC overrides for 200-300 seriesboards

"8086_a2af", Package()Most users on this forum, using Unibeast and Multibeast will expect to drop your Z370 USB ports.aml file into ACPI/patched and have sorted USB.

pastrychef

Moderator

- Joined

- May 29, 2013

- Messages

- 19,458

- Motherboard

- Mac Studio - Mac13,1

- CPU

- M1 Max

- Graphics

- 32 Core

- Mac

- Classic Mac

- Mobile Phone

Can you then please explain this method 2 clearly in your guide !!!! Also your Strix Z370 USB ports.aml file needs updating, tbh it's messy and your overrides is wrong for a start.

Code:// XHC overrides for 100-series boards "8086_a12f", Package()

Should be:

Code:// XHC overrides for 200-300 seriesboards "8086_a2af", Package()

Most users on this forum, using Unibeast and Multibeast will expect to drop your Z370 USB ports.aml file into ACPI/patched and have sorted USB.

You are right. I need to make that change. But I'm not going to mention every method possible to accomplish each goal.

Copyright © 2010 - 2024 tonymacx86 LLC