- Joined

- Jan 1, 2020

- Messages

- 615

- Motherboard

- MSI Z490 MPG Gaming Edge Wifi

- CPU

- i5-10600K

- Graphics

- RX 6600 XT

- Mac

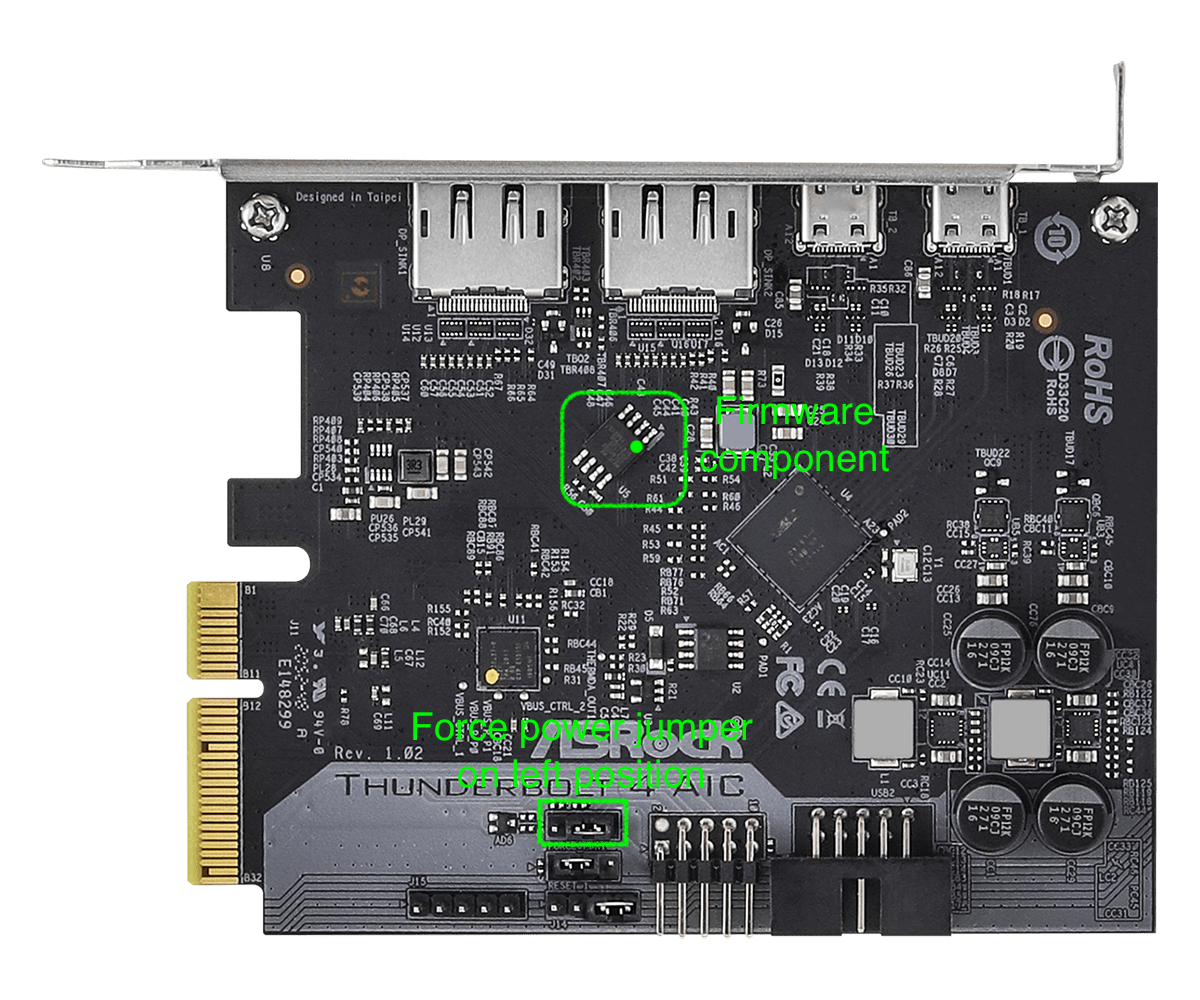

I have bought an Asrock Thunderbolt 4 AIC (Rev 1) with the following specification here :

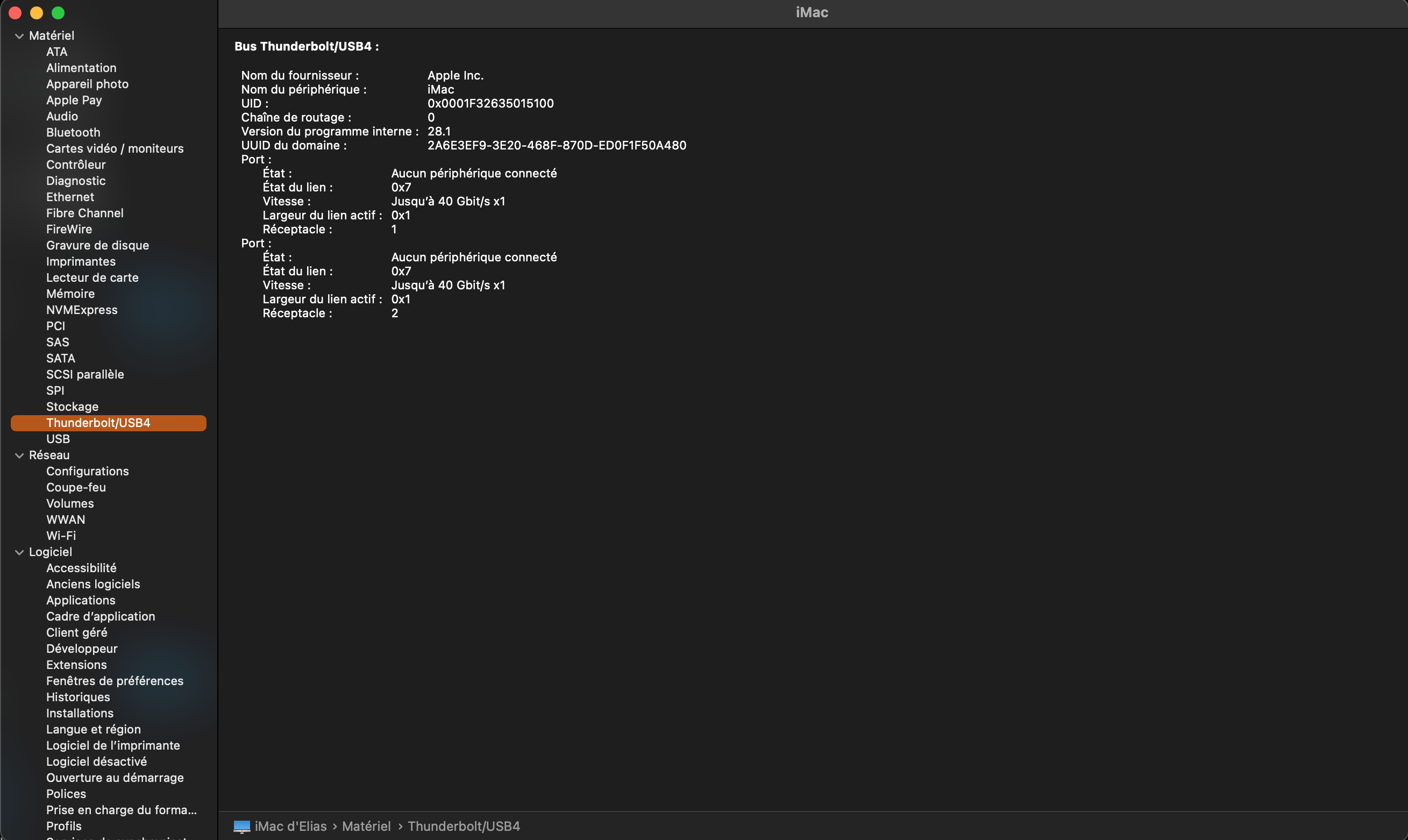

After patching firmware as usual (3 bytes similar to Thunderbolt 3 Titan Ridge)... et voila:

This AIC board have a TBTForcePower jumper, no external wire jumper needed.

Without a TBTHeader cable and plugged into an Asus B460M that doesn't include Thunderbolt setting (No TBT header and no TBT BIOS capabilities), it works fine (Hot-plug, Sleep/Wake, Alternate mode DisplayPort and 10Gbps USB-C).

Before firmware patching, Hot-plug wasn't working. It seems that macOS can drive Hot-plug capability very well... without AppleHPMIECS driver.

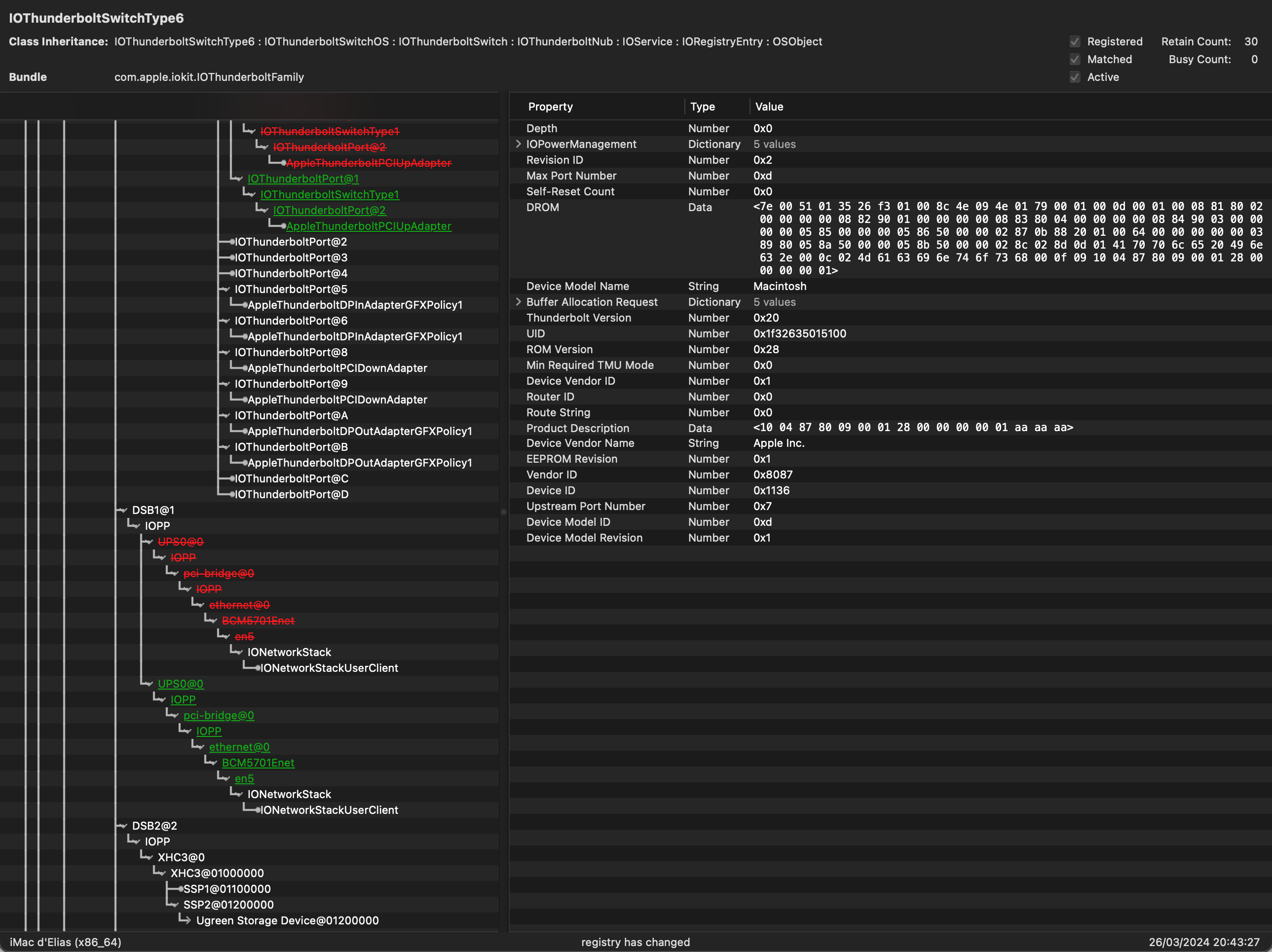

I also made 2 kernel patches to improve detection of "Complex" thunderbolt devices (that take more virtual memory like eGPU). "Simple" devices like Apple thunderbolt Ethernet (connected on previous screenshot) work without theses kernel patches.

Theses 2 patches consist on changing default IOThunderboltSwitchOS to IOThunderboltSwitchType6

For information, on disassembled code of IOThunderboltFamily, I also seen IOThunderboltSwitchJHL8440 .. I tried it, but I didn't have such as a good result as the SwitchType6

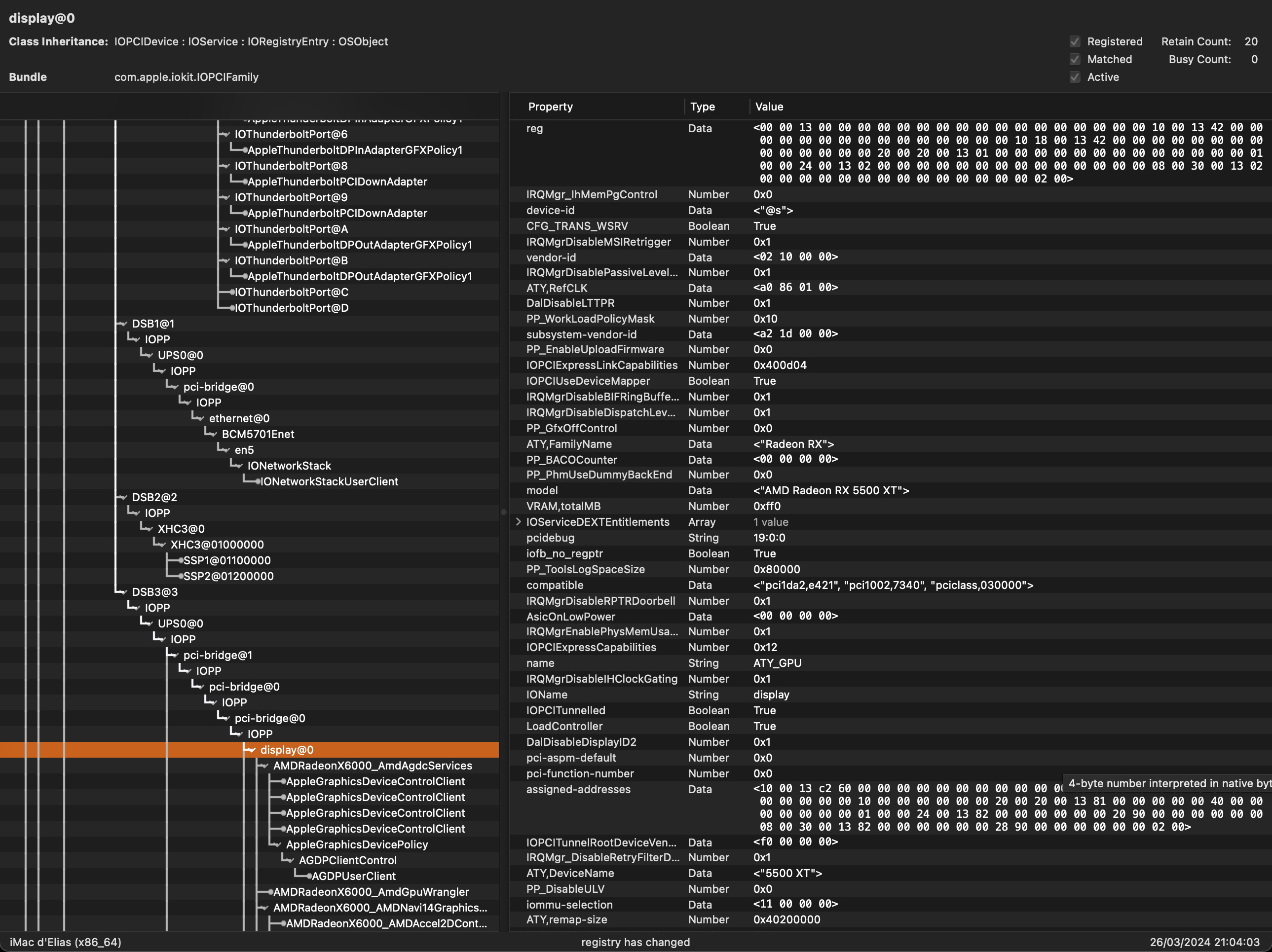

This last screen shot is with an AMD RX5500 XT graphic card embedded on eGPU :

Port@C and Port@D are USB4 adapters for AppleThunderboltUSBDownAdapter, I have enabled them on DROM (0x28C & 0x28D).. alas this driver plug-in is not available for Intel x86 platform (Apple Silicon only).. We should try an USB4 device that use PCIe bus to see what happen.

I have customised DROM part (at 0x4210 firmware address) before firmware flashing. You should do the same to customise your Thunderbolt UID (explain here). First byte at 0x4211 should remain at 0x00 if you have only one thunderbolt card.

Two lessons learned during reverse code investigations:

Other cards like ASUS Thunderbolt EX4 and Gigabyte GC-Maple Ridge could be tested like this.

I hope that Thunderbolt 5 (Barlow Ridge), expected in 2024, would be quite similar to Thunderbolt 3 & 4

EDIT:

Mistake on my first attached file, not fully patched ! Now it's OK.

After patching firmware as usual (3 bytes similar to Thunderbolt 3 Titan Ridge)... et voila:

This AIC board have a TBTForcePower jumper, no external wire jumper needed.

Without a TBTHeader cable and plugged into an Asus B460M that doesn't include Thunderbolt setting (No TBT header and no TBT BIOS capabilities), it works fine (Hot-plug, Sleep/Wake, Alternate mode DisplayPort and 10Gbps USB-C).

Before firmware patching, Hot-plug wasn't working. It seems that macOS can drive Hot-plug capability very well... without AppleHPMIECS driver.

I also made 2 kernel patches to improve detection of "Complex" thunderbolt devices (that take more virtual memory like eGPU). "Simple" devices like Apple thunderbolt Ethernet (connected on previous screenshot) work without theses kernel patches.

Theses 2 patches consist on changing default IOThunderboltSwitchOS to IOThunderboltSwitchType6

For information, on disassembled code of IOThunderboltFamily, I also seen IOThunderboltSwitchJHL8440 .. I tried it, but I didn't have such as a good result as the SwitchType6

This last screen shot is with an AMD RX5500 XT graphic card embedded on eGPU :

Port@C and Port@D are USB4 adapters for AppleThunderboltUSBDownAdapter, I have enabled them on DROM (0x28C & 0x28D).. alas this driver plug-in is not available for Intel x86 platform (Apple Silicon only).. We should try an USB4 device that use PCIe bus to see what happen.

I have customised DROM part (at 0x4210 firmware address) before firmware flashing. You should do the same to customise your Thunderbolt UID (explain here). First byte at 0x4211 should remain at 0x00 if you have only one thunderbolt card.

Two lessons learned during reverse code investigations:

- IOThunderboltSwitchOS & IOThunderboltSwitchType6 doesn't read ThunderboltDROM property unlike done with thunderbolt 3.

- TBTFlags property is required with minimum value of 0x8 (08 00 00 00) to load previous ThunderboltSwitches.

Other cards like ASUS Thunderbolt EX4 and Gigabyte GC-Maple Ridge could be tested like this.

I hope that Thunderbolt 5 (Barlow Ridge), expected in 2024, would be quite similar to Thunderbolt 3 & 4

EDIT:

Mistake on my first attached file, not fully patched ! Now it's OK.

Attachments

Last edited: