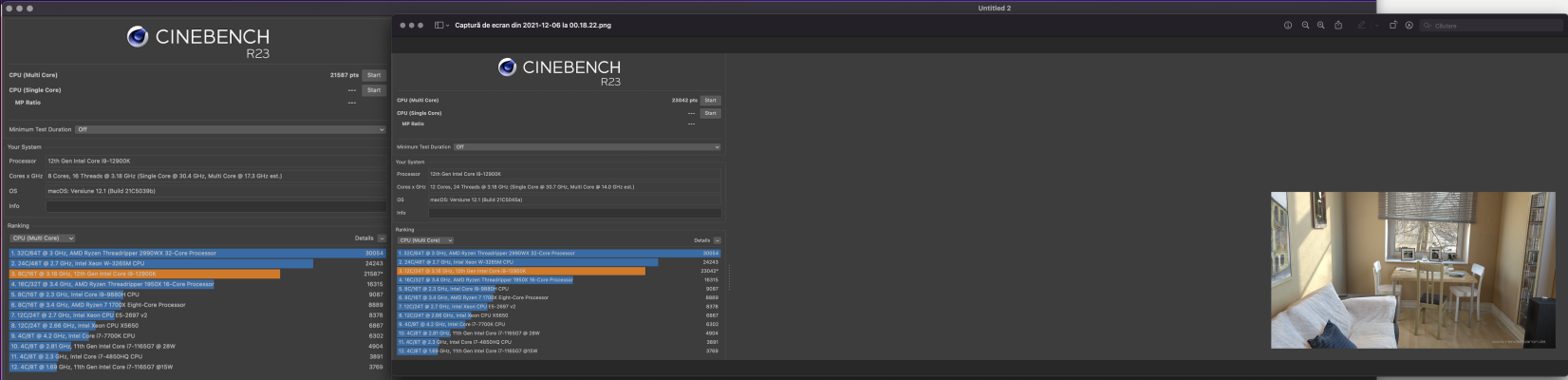

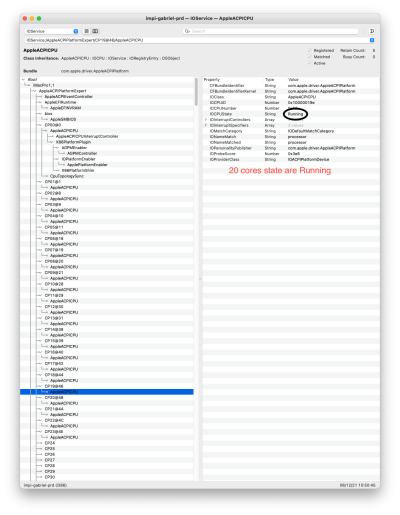

This suggests that the issue with the number of cores is not cosmetic and some E-cores remain inactive.

i5-12600K (6P+4E) should be 10C/16T, shows as 8C/14T in Geekbench (-2C/-2T). (

@CaseySJ )

i7-12700K (8P+4E) should be 12C/20T,

@Romanychev reports "+2 E-core", so I guess 10C/18T (-2C/-2T).

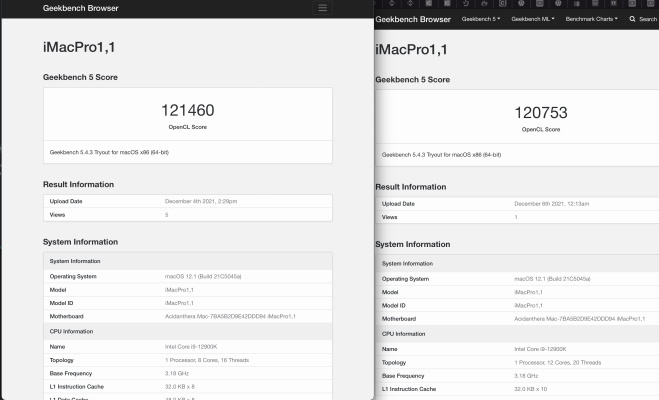

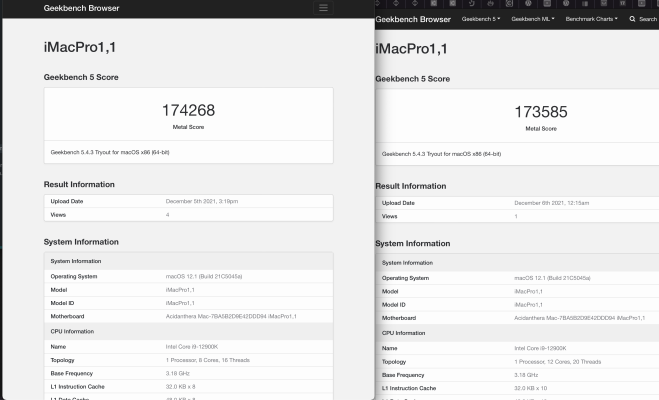

i9-12900K (8P+8E) should be 16C/24T, shows as 12C/20T in Geekbench (-4C/-4T). (

@StefanAM )

From previous experiments with SSDT-CPUR-Z690, we know that cores/threads appear in MADT in this order:

P1, PHT1, P2, PHT2,… Pn, HTn, E1, E2,…

and are allocated to \_SB_.PR## ACPI devices in this order.

SSDT-CPUR-Z690 wraps the ACPI devices to corresponding \_SB_.CP## processor objects.

SSDT-PLUG-ALT creates processor object stubs, without any reference to the actual ACPI processor devices; but apparently, OS X fills these stubs from MADT (including reading the actual Processor Base Address parameter from MADT rather than from the SSDT declaration).

What we see looks like OS X is creating phantom hyper-threads for the E-cores:

P1, PHT1, P2, PHT2,… E1,

EHT1, E2,

EHT2,…

@CaseySJ ,

@StefanAM ,

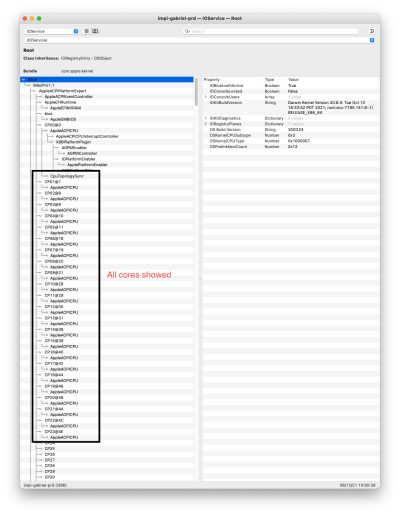

@Romanychev Can one of you post an IOReg with CpuTopologySync.kext in use? I'd like to see what the processors look like, especially the inactive ones.

www.tonymacx86.com