kgp

Retired

- Joined

- May 30, 2014

- Messages

- 6,743

- Motherboard

- ASUS WS X299 Sage 10G

- CPU

- i9-7980XE

- Graphics

- Vega 64

- Mac

- Mobile Phone

Ok...

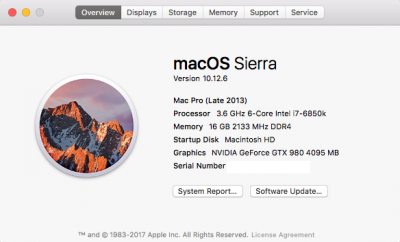

In any case, I was unable to activate the NVME on 10.12

I will try to install 10.13 on it to give you feedback and support your work!

In any case I can not work on 10.13 because there is still no support for the graphics card ...

And for me it's important that my work is video editing

But I'll update your manual and wait for an update of nvdia

thank you for the quick reply!

Perfect!

Many thanks for your support!