You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Quick Guide to Generate a SSDT for CPU Power Management

- Thread starter tonymacx86

- Start date

- Joined

- Feb 28, 2011

- Messages

- 25

- Motherboard

- ASUS ROG STRIXX Z390-E Gaming

- CPU

- i9 9900KF

- Graphics

- RTX2080 ti & RX 5700 XT

- Mac

- Mobile Phone

From a HP Pavilion 15-n056sf with Intel Core 1,6 GHz i5-4200U:

Code:

Settings:

------------------------------------

logMSRs............................: 1

logIGPU............................: 1

logIntelRegs.......................: 1

logCStates.........................: 1

logIPGStyle........................: 1

InitialTSC.........................: 0x6aa56609cd

MWAIT C-States.....................: 286531872

Model Specific Regiters

------------------------------------

MSR_CORE_THREAD_COUNT......(0x35) : 0x20004

MSR_PLATFORM_INFO..........(0xCE) : 0x8083DF3011700

MSR_PMG_CST_CONFIG_CONTROL.(0xE2) : 0x1E008408

MSR_PMG_IO_CAPTURE_BASE....(0xE4) : 0x51814

IA32_MPERF.................(0xE7) : 0x2417128294

IA32_APERF.................(0xE8) : 0x1FDBCF2501

MSR_FLEX_RATIO.............(0x194) : 0x0

MSR_IA32_PERF_STATUS.......(0x198) : 0x16C100000C00

MSR_IA32_PERF_CONTROL......(0x199) : 0xC00

IA32_CLOCK_MODULATION......(0x19A) : 0x8

IA32_THERM_STATUS..........(0x19C) : 0x88340000

IA32_MISC_ENABLES..........(0x1A0) : 0x850089

MSR_MISC_PWR_MGMT..........(0x1AA) : 0x400001

MSR_TURBO_RATIO_LIMIT......(0x1AD) : 0x1717171A

IA32_ENERGY_PERF_BIAS......(0x1B0) : 0xF

MSR_POWER_CTL..............(0x1FC) : 0x4005F

MSR_RAPL_POWER_UNIT........(0x606) : 0xA0E03

MSR_PKG_POWER_LIMIT........(0x610) : 0x804280C800DD80C8

MSR_PKG_ENERGY_STATUS......(0x611) : 0x167838C

MSR_PKG_POWER_INFO.........(0x614) : 0x78

MSR_PP0_CURRENT_CONFIG.....(0x601) : 0x4010141400000100

MSR_PP0_POWER_LIMIT........(0x638) : 0x0

MSR_PP0_ENERGY_STATUS......(0x639) : 0x8E1050

MSR_PP0_POLICY.............(0x63a) : 0x0

MSR_PP1_POWER_LIMIT........(0x640) : 0x0

MSR_PP1_ENERGY_STATUS......(0x641) : 0x5979C

MSR_PP1_POLICY.............(0x642) : 0x18

MSR_CONFIG_TDP_NOMINAL.....(0x648) : 0x10

MSR_CONFIG_TDP_LEVEL1......(0x649) : 0x8005C

MSR_CONFIG_TDP_LEVEL2......(0x64a) : 0x1700C8

MSR_CONFIG_TDP_CONTROL.....(0x64b) : 0x0

MSR_TURBO_ACTIVATION_RATIO.(0x64c) : 0x0

MSR_PKGC3_IRTL.............(0x60a) : 0x8842

MSR_PKGC6_IRTL.............(0x60b) : 0x8873

MSR_PKGC7_IRTL.............(0x60c) : 0x8891

MSR_PKG_C2_RESIDENCY.......(0x60d) : 0x26561B3933

MSR_PKG_C3_RESIDENCY.......(0x3f8) : 0x0

MSR_PKG_C6_RESIDENCY.......(0x3f9) : 0x0

MSR_PKG_C7_RESIDENCY.......(0x3fa) : 0x0

MSR_PKG_C8_RESIDENCY.......(0x630) : 0x0

MSR_PKG_C9_RESIDENCY.......(0x631) : 0x0

MSR_PKG_C10_RESIDENCY......(0x632) : 0x0

MSR_PKG_C8_LATENCY.........(0x633) : 0x0

MSR_PKG_C9_LATENCY.........(0x634) : 0x0

MSR_PKG_C10_LATENCY........(0x635) : 0x0

IA32_TSC_DEADLINE..........(0x6E0) : 0x6AD56BE931

PCH device.................: 0x9C438086

Intel Register Data

------------------------------------

CPU_VGACNTRL...............: 0x8000298E

IS_HASWELL(devid) || IS_BROADWELL(devid)

HSW_PWR_WELL_CTL1..........: 0xc0000000

HSW_PWR_WELL_CTL2..........: 0x40000000

HSW_PWR_WELL_CTL3..........: 0x40000000

HSW_PWR_WELL_CTL4..........: 0x40000000

HSW_PWR_WELL_CTL5..........: 0x0004050f

HSW_PWR_WELL_CTL6..........: 0x00000000

PIPE_DDI_FUNC_CTL_A........: 0x91200000 (enabled, DDIB, DVI, 6 bpc, -VSync, -HSync, EDP A ON, x1)

PIPE_DDI_FUNC_CTL_B........: 0x00030000 (disabled, no port, HDMI, 8 bpc, +VSync, +HSync, EDP A ON, x1)

PIPE_DDI_FUNC_CTL_C........: 0x00030000 (disabled, no port, HDMI, 8 bpc, +VSync, +HSync, EDP A ON, x1)

PIPE_DDI_FUNC_CTL_EDP......: 0x82234000 (enabled, no port, DP SST, 6 bpc, +VSync, +HSync, EDP A ONOFF, x1)

DP_TP_CTL_A................: 0x80040300

DP_TP_CTL_B................: 0x00000000

DP_TP_CTL_C................: 0x00000000

DP_TP_CTL_D................: 0x00000000

DP_TP_CTL_E................: 0x00000000

DP_TP_STATUS_A.............: 0x00000000

DP_TP_STATUS_B.............: 0x00000000

DP_TP_STATUS_C.............: 0x00000000

DP_TP_STATUS_D.............: 0x00000000

DP_TP_STATUS_E.............: 0x00000000

DDI_BUF_CTL_A..............: 0x80000011 (enabled not reversed x1 detected)

DDI_BUF_CTL_B..............: 0x00000000 (disabled not reversed x1 not detected)

DDI_BUF_CTL_C..............: 0x00000000 (disabled not reversed x1 not detected)

DDI_BUF_CTL_D..............: 0x00000000 (disabled not reversed x1 not detected)

DDI_BUF_CTL_E..............: 0x00000080 (disabled not reversed x1 not detected)

SPLL_CTL...................: 0x00000000

LCPLL_CTL..................: 0x40000037

WRPLL_CTL1.................: 0x90280202

WRPLL_CTL2.................: 0x00202418

PORT_CLK_SEL_A.............: 0x80000000 (WRPLL 1)

PORT_CLK_SEL_B.............: 0xe0000000 (None)

PORT_CLK_SEL_C.............: 0xe0000000 (None)

PORT_CLK_SEL_D.............: 0xe0000000 (None)

PORT_CLK_SEL_E.............: 0xe0000000 (None)

PIPE_CLK_SEL_A.............: 0x00000000 (None)

PIPE_CLK_SEL_B.............: 0x00000000 (None)

PIPE_CLK_SEL_C.............: 0x00000000 (None)

SFUSE_STRAP................: 0x00000004 (display enabled, crt no, lane reversal no, port b yes, port c no, port d no)

PIPEASRC...................: 0x055502ff (1366, 768)

DSPACNTR...................: 0xd8000400 (enabled)

DSPASTRIDE.................: 0x00001600 (88)

DSPASURF...................: 0x10580000

DSPATILEOFF................: 0x00000000 (0, 0)

PIPEBSRC...................: 0x00000000 (1, 1)

DSPBCNTR...................: 0x00000000 (disabled)

DSPBSTRIDE.................: 0x00000000 (0)

DSPBSURF...................: 0x00000000

DSPBTILEOFF................: 0x00000000 (0, 0)

PIPECSRC...................: 0x00000000 (1, 1)

DSPCCNTR...................: 0x00000000 (disabled)

DSPCSTRIDE.................: 0x00000000 (0)

DSPCSURF...................: 0x00000000

DSPCTILEOFF................: 0x00000000 (0, 0)

PIPEACONF..................: 0x00000000 (disabled, inactive, pf-pd, rotate 0, 8bpc)

HTOTAL_A...................: 0x06370555 (1366 active, 1592 total)

HBLANK_A...................: 0x06370555 (1366 start, 1592 end)

HSYNC_A....................: 0x0591057b (1404 start, 1426 end)

VTOTAL_A...................: 0x031d02ff (768 active, 798 total)

VBLANK_A...................: 0x031d02ff (768 start, 798 end)

VSYNC_A....................: 0x03080302 (771 start, 777 end)

VSYNCSHIFT_A...............: 0x00000000

PIPEA_DATA_M1..............: 0x00000000 (TU 1, val 0x0 0)

PIPEA_DATA_N1..............: 0x00000000 (val 0x0 0)

PIPEA_LINK_M1..............: 0x00000000 (val 0x0 0)

PIPEA_LINK_N1..............: 0x00000000 (val 0x0 0)

PIPEBCONF..................: 0x00000000 (disabled, inactive, pf-pd, rotate 0, 8bpc)

HTOTAL_B...................: 0x00000000 (1 active, 1 total)

HBLANK_B...................: 0x00000000 (1 start, 1 end)

HSYNC_B....................: 0x00000000 (1 start, 1 end)

VTOTAL_B...................: 0x00000000 (1 active, 1 total)

VBLANK_B...................: 0x00000000 (1 start, 1 end)

VSYNC_B....................: 0x00000000 (1 start, 1 end)

VSYNCSHIFT_B...............: 0x00000000

PIPEB_DATA_M1..............: 0x00000000 (TU 1, val 0x0 0)

PIPEB_DATA_N1..............: 0x00000000 (val 0x0 0)

PIPEB_LINK_M1..............: 0x00000000 (val 0x0 0)

PIPEB_LINK_N1..............: 0x00000000 (val 0x0 0)

PIPECCONF..................: 0x00000000 (disabled, inactive, pf-pd, rotate 0, 8bpc)

HTOTAL_C...................: 0x00000000 (1 active, 1 total)

HBLANK_C...................: 0x00000000 (1 start, 1 end)

HSYNC_C....................: 0x00000000 (1 start, 1 end)

VTOTAL_C...................: 0x00000000 (1 active, 1 total)

VBLANK_C...................: 0x00000000 (1 start, 1 end)

VSYNC_C....................: 0x00000000 (1 start, 1 end)

VSYNCSHIFT_C...............: 0x00000000

PIPEC_DATA_M1..............: 0x00000000 (TU 1, val 0x0 0)

PIPEC_DATA_N1..............: 0x00000000 (val 0x0 0)

PIPEC_LINK_M1..............: 0x00000000 (val 0x0 0)

PIPEC_LINK_N1..............: 0x00000000 (val 0x0 0)

PIPEEDPCONF................: 0xc0000010 (enabled, active, pf-pd, rotate 0, 8bpc)

HTOTAL_EDP.................: 0x06370555 (1366 active, 1592 total)

HBLANK_EDP.................: 0x06370555 (1366 start, 1592 end)

HSYNC_EDP..................: 0x0591057b (1404 start, 1426 end)

VTOTAL_EDP.................: 0x031d02ff (768 active, 798 total)

VBLANK_EDP.................: 0x031d02ff (768 start, 798 end)

VSYNC_EDP..................: 0x03080302 (771 start, 777 end)

VSYNCSHIFT_EDP.............: 0x00000000

PIPEEDP_DATA_M1............: 0x7e5196de (TU 64, val 0x5196de 5347038)

PIPEEDP_DATA_N1............: 0x00800000 (val 0x800000 8388608)

PIPEEDP_LINK_M1............: 0x00024430 (val 0x24430 148528)

PIPEEDP_LINK_N1............: 0x00080000 (val 0x80000 524288)

PFA_CTL_1..................: 0x00000000 (disable, auto_scale yes, auto_scale_cal no, v_filter enable, vadapt disable, mode least, filter_sel programmed,chroma pre-filter disable, vert3tap auto, v_inter_invert field 1)

PFA_WIN_POS................: 0x00000000 (0, 0)

PFA_WIN_SIZE...............: 0x00000000 (0, 0)

PFB_CTL_1..................: 0x00000000 (disable, auto_scale yes, auto_scale_cal no, v_filter enable, vadapt disable, mode least, filter_sel programmed,chroma pre-filter disable, vert3tap auto, v_inter_invert field 1)

PFB_WIN_POS................: 0x00000000 (0, 0)

PFB_WIN_SIZE...............: 0x00000000 (0, 0)

PFC_CTL_1..................: 0x00000000 (disable, auto_scale yes, auto_scale_cal no, v_filter enable, vadapt disable, mode least, filter_sel programmed,chroma pre-filter disable, vert3tap auto, v_inter_invert field 1)

PFC_WIN_POS................: 0x00000000 (0, 0)

PFC_WIN_SIZE...............: 0x00000000 (0, 0)

TRANS_HTOTAL_A.............: 0x00000000 (1 active, 1 total)

TRANS_HBLANK_A.............: 0x00000000 (1 start, 1 end)

TRANS_HSYNC_A..............: 0x00000000 (1 start, 1 end)

TRANS_VTOTAL_A.............: 0x00000000 (1 active, 1 total)

TRANS_VBLANK_A.............: 0x00000000 (1 start, 1 end)

TRANS_VSYNC_A..............: 0x00000000 (1 start, 1 end)

TRANS_VSYNCSHIFT_A.........: 0x00000000

TRANSACONF.................: 0x00000000 (disable, inactive, progressive)

FDI_RXA_MISC...............: 0x00000000 (FDI Delay 0)

FDI_RXA_TUSIZE1............: 0x00000000

FDI_RXA_IIR................: 0x00000000

FDI_RXA_IMR................: 0x00000000

BLC_PWM_CPU_CTL2...........: 0x80000000 (enable 1, pipe A, blinking 0, granularity 128)

BLC_PWM_CPU_CTL............: 0x03a903a9 (cycle 937, freq 937)

BLC_PWM2_CPU_CTL2..........: 0x60000000 (enable 0, pipe EDP, blinking 0, granularity 128)

BLC_PWM2_CPU_CTL...........: 0x00000000 (cycle 0, freq 0)

BLC_MISC_CTL...............: 0x00000000 (PWM1-PCH PWM2-CPU)

BLC_PWM_PCH_CTL1...........: 0xc0000000 (enable 1, override 1, inverted polarity 0)

BLC_PWM_PCH_CTL2...........: 0x0ad90ad9 (freq 2777, cycle 2777)

UTIL_PIN_CTL...............: 0x00000000 (enable 0, transcoder A, mode data, data 0 inverted polarity 0)

PCH_PP_STATUS..............: 0x80000008 (on, not ready, sequencing idle)

PCH_PP_CONTROL.............: 0xabcd0007 (blacklight enabled, power down on reset, panel on)

PCH_PP_ON_DELAYS...........: 0x07d00000

PCH_PP_OFF_DELAYS..........: 0x01f407d0

PCH_PP_DIVISOR.............: 0x0004af06

PIXCLK_GATE................: 0x0004af06

SDEISR.....................: 0x00c00000 (port d:1, port c:1, port b:0, crt:0)

RC6_RESIDENCY_TIME.........: 0x087296a9

IS_GEN6(devid) || IS_GEN7(devid)

FENCE START 0..............: 0x00000001

FENCE END 0................: 0x012ff02b

FENCE START 1..............: 0x00000000

FENCE END 1................: 0x00000000

FENCE START 2..............: 0x00000000

FENCE END 2................: 0x00000000

FENCE START 3..............: 0x00000000

FENCE END 3................: 0xfffff3ff

FENCE START 4..............: 0x00000000

FENCE END 4................: 0x00000000

FENCE START 5..............: 0x00000000

FENCE END 5................: 0x00000000

FENCE START 6..............: 0x00000000

FENCE END 6................: 0x00000000

FENCE START 7..............: 0x00000000

FENCE END 7................: 0x00000000

FENCE START 8..............: 0x00000000

FENCE END 8................: 0x00000000

FENCE START 9..............: 0x00000000

FENCE END 9................: 0x00000000

FENCE START 10.............: 0x00000000

FENCE END 10...............: 0x00000000

FENCE START 11.............: 0x00000000

FENCE END 11...............: 0x00000000

FENCE START 12.............: 0x00000000

FENCE END 12...............: 0x00000000

FENCE START 13.............: 0x00000000

FENCE END 13...............: 0x00000000

FENCE START 14.............: 0x00000000

FENCE END 14...............: 0x00000000

FENCE START 15.............: 0x00000000

FENCE END 15...............: 0x00000000

FENCE START 16.............: 0x00000000

FENCE END 16...............: 0x00000000

FENCE START 17.............: 0x00000000

FENCE END 17...............: 0x00000000

FENCE START 18.............: 0x00000000

FENCE END 18...............: 0x00000000

FENCE START 19.............: 0x00000000

FENCE END 19...............: 0x00000000

FENCE START 20.............: 0x00000000

FENCE END 20...............: 0x00000000

FENCE START 20.............: 0x00000000

FENCE END 20...............: 0x00000000

FENCE START 21.............: 0x00000000

FENCE END 21...............: 0x00000000

FENCE START 22.............: 0x00000000

FENCE END 22...............: 0x00000000

FENCE START 23.............: 0x00000000

FENCE END 23...............: 0x00000000

FENCE START 24.............: 0x00000000

FENCE END 24...............: 0x00000000

FENCE START 25.............: 0x00000000

FENCE END 25...............: 0x00000000

FENCE START 26.............: 0x00000000

FENCE END 26...............: 0x00000000

FENCE START 27.............: 0x00000000

FENCE END 27...............: 0x00000000

FENCE START 28.............: 0x00000000

FENCE END 28...............: 0x00000000

FENCE START 29.............: 0x00000000

FENCE END 29...............: 0x00000000

FENCE START 30.............: 0x00000000

FENCE END 30...............: 0x00000000

FENCE START 31.............: 0x00000000

FENCE END 31...............: 0x00000000

GEN6_RP_CONTROL............: 0x00000000 (disabled)

GEN6_RPNSWREQ..............: 0x00000000

GEN6_RP_DOWN_TIMEOUT.......: 0x00000000

GEN6_RP_INTERRUPT_LIMITS...: 0x00000000

GEN6_RP_UP_THRESHOLD.......: 0x00000000

GEN6_RP_UP_EI..............: 0x00000000

GEN6_RP_DOWN_EI............: 0x00000000

GEN6_RP_IDLE_HYSTERSIS.....: 0x00000000

GEN6_RC_STATE..............: 0x00000000

GEN6_RC_CONTROL............: 0x00000000

GEN6_RC1_WAKE_RATE_LIMIT...: 0x00000000

GEN6_RC6_WAKE_RATE_LIMIT...: 0x00000000

GEN6_RC_EVALUATION_INTERVAL: 0x00000000

GEN6_RC_IDLE_HYSTERSIS.....: 0x00000000

GEN6_RC_SLEEP..............: 0x00000000

GEN6_RC1e_THRESHOLD........: 0x00000000

GEN6_RC6_THRESHOLD.........: 0x00000000

GEN6_RC_VIDEO_FREQ.........: 0x00000000

GEN6_PMIER.................: 0x00000430

GEN6_PMIMR.................: 0x00000000

GEN6_PMINTRMSK.............: 0x00000000

CPU Ratio Info:

------------------------------------

CPU Low Frequency Mode.............: 800 MHz

CPU Maximum non-Turbo Frequency....: 2300 MHz

CPU Maximum Turbo Frequency........: 2600 MHz

IGPU Info:

------------------------------------

IGPU Current Frequency.............: 200 MHz

IGPU Minimum Frequency.............: 200 MHz

IGPU Maximum Non-Turbo Frequency...: 200 MHz

IGPU Maximum Turbo Frequency.......: 1000 MHz

IGPU Maximum limit.................: No Limit

CPU P-States [ 12 (16) 20 ] iGPU P-States [ (4) ]

CPU C3-Cores [ 0 1 2 3 ]

CPU C6-Cores [ 0 1 2 3 ]

CPU C7-Cores [ 0 1 2 3 ]

CPU P-States [ (8) 12 16 19 20 ] iGPU P-States [ (4) ]

CPU P-States [ (8) 10 12 16 19 20 ] iGPU P-States [ (4) ]

CPU P-States [ 8 10 (12) 13 16 19 20 ] iGPU P-States [ (4) ]

CPU P-States [ (8) 10 12 13 16 19 20 22 ] iGPU P-States [ (4) ]

CPU P-States [ 8 10 (12) 13 14 16 19 20 22 ] iGPU P-States [ (4) ]

CPU P-States [ 8 10 (12) 13 14 15 16 19 20 22 ] iGPU P-States [ (4) ]

CPU P-States [ (8) 10 11 12 13 14 15 16 19 20 22 ] iGPU P-States [ (4) ]- Joined

- Jun 1, 2011

- Messages

- 12

- Motherboard

- Dell XPS 7590

- CPU

- i7-9750H

- Graphics

- UHD 630 + GTX 1650

- Mobile Phone

After creating the ssdt files I get better speedsteps but also artifacts on my HD3000. Could there be a relation between both? I have hd3000 with discrete 540m (disabled through dsdt)

- Joined

- Jan 16, 2011

- Messages

- 557

- Motherboard

- Asus ROG MAXIMUS X HERO

- CPU

- i7-9700K

- Graphics

- RX 580

- Mac

- Classic Mac

- Mobile Phone

A new log line is output whenever the output is different from the last. The latest represents the cumulative "pstates seen" since the beginning.

Thank you for this explanation.

I was quite disappointed from the results I got right after I generated the new ssdt:

Code:

CPU Ratio Info:

------------------------------------

CPU Low Frequency Mode.............: 1600 MHz

CPU Maximum non-Turbo Frequency....: 3400 MHz

CPU Maximum Turbo Frequency........: 3800 MHz

CPU P-States [ (17) 30 ]

CPU C3-Cores [ 3 4 5 ]

CPU C6-Cores [ 1 2 3 4 7 ]

CPU P-States [ (17) 30 32 ]

CPU C6-Cores [ 1 2 3 4 5 7 ]

CPU P-States [ (16) 17 30 32 ]

CPU C3-Cores [ 3 4 5 6 7 ]

CPU C6-Cores [ 1 2 3 4 5 6 7 ]

CPU C3-Cores [ 2 3 4 5 6 7 ]

CPU C6-Cores [ 0 1 2 3 4 5 6 7 ]

CPU C3-Cores [ 0 2 3 4 5 6 7 ]

CPU C3-Cores [ 0 1 2 3 4 5 6 7 ]

CPU P-States [ 16 (17) 19 30 32 ]

CPU P-States [ 16 (17) 19 20 30 32 ]

CPU P-States [ 16 (17) 18 19 20 30 32 ]But after what you wrote I thought it would be a good idea to run the same command once again.

This is what I got in the second run, using the same ssdt as before:

Code:

CPU Ratio Info:

------------------------------------

CPU Low Frequency Mode.............: 1600 MHz

CPU Maximum non-Turbo Frequency....: 3400 MHz

CPU Maximum Turbo Frequency........: 3800 MHz

CPU P-States [ (17) 30 ]

CPU C3-Cores [ 3 4 5 ]

CPU C6-Cores [ 1 2 3 4 7 ]

CPU P-States [ (17) 30 32 ]

CPU C6-Cores [ 1 2 3 4 5 7 ]

CPU P-States [ (16) 17 30 32 ]

CPU C3-Cores [ 3 4 5 6 7 ]

CPU C6-Cores [ 1 2 3 4 5 6 7 ]

CPU C3-Cores [ 2 3 4 5 6 7 ]

CPU C6-Cores [ 0 1 2 3 4 5 6 7 ]

CPU C3-Cores [ 0 2 3 4 5 6 7 ]

CPU C3-Cores [ 0 1 2 3 4 5 6 7 ]

CPU P-States [ 16 (17) 19 30 32 ]

CPU P-States [ 16 (17) 19 20 30 32 ]

CPU P-States [ 16 (17) 18 19 20 30 32 ]

CPU P-States [ 16 (17) 18 19 20 30 32 34 ]

CPU P-States [ 16 (17) 18 19 20 21 30 32 34 ]

CPU P-States [ 16 (17) 18 19 20 21 26 30 32 34 ]

CPU P-States [ 16 17 18 19 20 21 26 30 32 34 35 (36) ]

CPU P-States [ 16 17 18 19 20 21 26 30 32 33 34 35 36 (37) ]

CPU P-States [ (16) 17 18 19 20 21 26 27 30 32 33 34 35 36 37 ]

CPU P-States [ 16 (17) 18 19 20 21 26 27 29 30 32 33 34 35 36 37 ]

CPU P-States [ 16 (17) 18 19 20 21 25 26 27 29 30 32 33 34 35 36 37 ]

CPU P-States [ 16 (17) 18 19 20 21 25 26 27 29 30 31 32 33 34 35 36 37 ]

CPU P-States [ 16 (17) 18 19 20 21 24 25 26 27 29 30 31 32 33 34 35 36 37 ]

CPU P-States [ 16 (17) 18 19 20 21 22 24 25 26 27 29 30 31 32 33 34 35 36 37 ]

CPU P-States [ 16 (17) 18 19 20 21 22 23 24 25 26 27 29 30 31 32 33 34 35 36 37 ]

CPU P-States [ 16 (17) 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 ]I am ... impressed. Or does this look too nice and I am fooled by a mistake of mine?

- Joined

- Jul 20, 2011

- Messages

- 22

- Motherboard

- z68ma d2h b3

- CPU

- I5 2500

- Graphics

- GT430 Nvidia

- Mac

- Classic Mac

- Mobile Phone

Code:

Settings:

------------------------------------

logMSRs............................: 1

logIGPU............................: 0

logIntelRegs.......................: 1

logCStates.........................: 1

logIPGStyle........................: 1

InitialTSC.........................: 0x6f92d94a79

MWAIT C-States.....................: 4384

Model Specific Regiters

------------------------------------

MSR_CORE_THREAD_COUNT......(0x35) : 0x40004

MSR_PLATFORM_INFO..........(0xCE) : 0x100070012100

MSR_PMG_CST_CONFIG_CONTROL.(0xE2) : 0x18000403

MSR_PMG_IO_CAPTURE_BASE....(0xE4) : 0x10414

IA32_MPERF.................(0xE7) : 0x2A9DB713AC

IA32_APERF.................(0xE8) : 0x2B2573C37A

MSR_FLEX_RATIO.............(0x194) : 0x80000

MSR_IA32_PERF_STATUS.......(0x198) : 0x288300002200

MSR_IA32_PERF_CONTROL......(0x199) : 0x2300

IA32_CLOCK_MODULATION......(0x19A) : 0x0

IA32_THERM_STATUS..........(0x19C) : 0x88200000

IA32_MISC_ENABLES..........(0x1A0) : 0x850089

MSR_MISC_PWR_MGMT..........(0x1AA) : 0x400001

MSR_TURBO_RATIO_LIMIT......(0x1AD) : 0x22232425

IA32_ENERGY_PERF_BIAS......(0x1B0) : 0x4

MSR_POWER_CTL..............(0x1FC) : 0x4005F

MSR_RAPL_POWER_UNIT........(0x606) : 0xA1003

MSR_PKG_POWER_LIMIT........(0x610) : 0xA58000009F40

MSR_PKG_ENERGY_STATUS......(0x611) : 0x1243608A

MSR_PKG_POWER_INFO.........(0x614) : 0x1E002F8

MSR_PP0_CURRENT_CONFIG.....(0x601) : 0x1814149400000960

MSR_PP0_POWER_LIMIT........(0x638) : 0xA580

MSR_PP0_ENERGY_STATUS......(0x639) : 0xF398E33

MSR_PP0_POLICY.............(0x63a) : 0x0

MSR_PKGC3_IRTL.............(0x60a) : 0x8850

MSR_PKGC6_IRTL.............(0x60b) : 0x8868

MSR_PKGC7_IRTL.............(0x60c) : 0x886D

MSR_PKG_C2_RESIDENCY.......(0x60d) : 0x79886DDEC

MSR_PKG_C3_RESIDENCY.......(0x3f8) : 0x0

MSR_PKG_C6_RESIDENCY.......(0x3f9) : 0x38140338F

MSR_PKG_C7_RESIDENCY.......(0x3fa) : 0x0

IA32_TSC_DEADLINE..........(0x6E0) : 0x6F955DA502

CPU Ratio Info:

------------------------------------

CPU Low Frequency Mode.............: 1600 MHz

CPU Maximum non-Turbo Frequency....: 3300 MHz

CPU Maximum Turbo Frequency........: 3700 MHz

CPU P-States [ (34) ]

CPU C6-Cores [ 0 2 3 ]

CPU C6-Cores [ 0 1 2 3 ]

CPU P-States [ 33 34 (35) ]

CPU P-States [ 33 34 35 (36) ]

CPU P-States [ (16) 33 34 35 36 ]

CPU P-States [ (16) 31 33 34 35 36 ]P-States it come to put at 67x. there is nothing in the range 20x. any help?

- Joined

- Oct 20, 2010

- Messages

- 18

- Motherboard

- Gigabyte z68ma-d2h-b3

- CPU

- 2400 << need model # >> See Forum Rules !!

- Graphics

- << need model # >> See Forum Rules !!

- Mac

- Mobile Phone

I generated an SSDT for my old i52400,but temps where higher with the SSDT. So i checked "generate p states" and "drop oem" with clover. It gave me less states but temps are OK now.

- Joined

- Nov 11, 2013

- Messages

- 14

- Motherboard

- Z68XP-UD5 F6

- CPU

- i7-2700K

- Graphics

- AMD Radeon HD 6870

- Mac

- Classic Mac

- Mobile Phone

I followed the guide but im only showing 2 states? is this correct?

i7-2600K

i7-2600K

Code:

AppleIntelInfo.kext v1.2 Copyright © 2012-2015 Pike R. Alpha. All rights reserved

Settings:

------------------------------------

logMSRs............................: 1

logIGPU............................: 0

logIntelRegs.......................: 1

logCStates.........................: 1

logIPGStyle........................: 1

InitialTSC.........................: 0x7c84ceb9f6

MWAIT C-States.....................: 4384

Model Specific Regiters

------------------------------------

MSR_CORE_THREAD_COUNT......(0x35) : 0x40008

MSR_PLATFORM_INFO..........(0xCE) : 0x100070012200

MSR_PMG_CST_CONFIG_CONTROL.(0xE2) : 0x1E000403

MSR_PMG_IO_CAPTURE_BASE....(0xE4) : 0x20414

IA32_MPERF.................(0xE7) : 0x316737E3FC

IA32_APERF.................(0xE8) : 0x32C4CA9B61

MSR_FLEX_RATIO.............(0x194) : 0xE0000

MSR_IA32_PERF_STATUS.......(0x198) : 0x280800002300

MSR_IA32_PERF_CONTROL......(0x199) : 0x2600

IA32_CLOCK_MODULATION......(0x19A) : 0x8

IA32_THERM_STATUS..........(0x19C) : 0x88370000

IA32_MISC_ENABLES..........(0x1A0) : 0x850081

MSR_MISC_PWR_MGMT..........(0x1AA) : 0x0

MSR_TURBO_RATIO_LIMIT......(0x1AD) : 0x23242526

IA32_ENERGY_PERF_BIAS......(0x1B0) : 0x0

MSR_POWER_CTL..............(0x1FC) : 0x4005C

MSR_RAPL_POWER_UNIT........(0x606) : 0xA1003

MSR_PKG_POWER_LIMIT........(0x610) : 0xA58000008960

MSR_PKG_ENERGY_STATUS......(0x611) : 0x1868AE2B

MSR_PKG_POWER_INFO.........(0x614) : 0x1E002F8

MSR_PP0_CURRENT_CONFIG.....(0x601) : 0x18141494000008C0

MSR_PP0_POWER_LIMIT........(0x638) : 0x8960

MSR_PP0_ENERGY_STATUS......(0x639) : 0x144E8AA8

MSR_PP0_POLICY.............(0x63a) : 0x1F

MSR_PKGC3_IRTL.............(0x60a) : 0x8C02

MSR_PKGC6_IRTL.............(0x60b) : 0x8854

MSR_PKGC7_IRTL.............(0x60c) : 0x8854

MSR_PKG_C2_RESIDENCY.......(0x60d) : 0x0

MSR_PKG_C3_RESIDENCY.......(0x3f8) : 0x0

MSR_PKG_C6_RESIDENCY.......(0x3f9) : 0x0

MSR_PKG_C7_RESIDENCY.......(0x3fa) : 0x0

IA32_TSC_DEADLINE..........(0x6E0) : 0x7C87555B4B

CPU Ratio Info:

------------------------------------

CPU Low Frequency Mode.............: 1600 MHz

CPU Maximum non-Turbo Frequency....: 3400 MHz

CPU Maximum Turbo Frequency........: 3800 MHz

CPU P-States [ 33 (35) ]- Joined

- Feb 5, 2013

- Messages

- 50

- Motherboard

- GA-Z97X-UD3H-BK

- CPU

- i5-4590

- Graphics

- RX-580

- Mobile Phone

I got full states but not sure what need to set up in clover ACPI setting. I saw some one has DSDT patches there but I don't have it. I just following the guide and copy DSDT.aml to patched folder. rebooting the system a few time I am still getting full states.

==================================================

==================================================

Code:

AppleIntelInfo.kext v1.2 Copyright © 2012-2015 Pike R. Alpha. All rights reserved

Settings:

------------------------------------

logMSRs............................: 1

logIGPU............................: 0

logIntelRegs.......................: 1

logCStates.........................: 1

logIPGStyle........................: 1

InitialTSC.........................: 0x29a50d4ef1b

MWAIT C-States.....................: 270624

Model Specific Regiters

------------------------------------

MSR_CORE_THREAD_COUNT......(0x35) : 0x40004

MSR_PLATFORM_INFO..........(0xCE) : 0x80838F3012100

MSR_PMG_CST_CONFIG_CONTROL.(0xE2) : 0x1E000402

MSR_PMG_IO_CAPTURE_BASE....(0xE4) : 0x1814

IA32_MPERF.................(0xE7) : 0x20A38245F2

IA32_APERF.................(0xE8) : 0x211550C930

MSR_FLEX_RATIO.............(0x194) : 0x0

MSR_IA32_PERF_STATUS.......(0x198) : 0x221B00002300

MSR_IA32_PERF_CONTROL......(0x199) : 0x2500

IA32_CLOCK_MODULATION......(0x19A) : 0x0

IA32_THERM_STATUS..........(0x19C) : 0x88480000

IA32_MISC_ENABLES..........(0x1A0) : 0x850089

MSR_MISC_PWR_MGMT..........(0x1AA) : 0x1

MSR_TURBO_RATIO_LIMIT......(0x1AD) : 0x25252525

IA32_ENERGY_PERF_BIAS......(0x1B0) : 0x1

MSR_POWER_CTL..............(0x1FC) : 0x4005F

MSR_RAPL_POWER_UNIT........(0x606) : 0xA0E03

MSR_PKG_POWER_LIMIT........(0x610) : 0xFFD00000EA82

MSR_PKG_ENERGY_STATUS......(0x611) : 0x7534AFA

MSR_PKG_POWER_INFO.........(0x614) : 0x2A0

MSR_PP0_CURRENT_CONFIG.....(0x601) : 0x1F40

MSR_PP0_POWER_LIMIT........(0x638) : 0xFFD0

MSR_PP0_ENERGY_STATUS......(0x639) : 0x204F658

MSR_PP0_POLICY.............(0x63a) : 0x0

MSR_CONFIG_TDP_NOMINAL.....(0x648) : 0x21

MSR_CONFIG_TDP_LEVEL1......(0x649) : 0x0

MSR_CONFIG_TDP_LEVEL2......(0x64a) : 0x0

MSR_CONFIG_TDP_CONTROL.....(0x64b) : 0x80000000

MSR_TURBO_ACTIVATION_RATIO.(0x64c) : 0x0

MSR_PKGC3_IRTL.............(0x60a) : 0x8842

MSR_PKGC6_IRTL.............(0x60b) : 0x8873

MSR_PKGC7_IRTL.............(0x60c) : 0x8891

MSR_PKG_C2_RESIDENCY.......(0x60d) : 0x214FA5B10FE

MSR_PKG_C3_RESIDENCY.......(0x3f8) : 0x0

MSR_PKG_C6_RESIDENCY.......(0x3f9) : 0x0

MSR_PKG_C7_RESIDENCY.......(0x3fa) : 0x0

IA32_TSC_DEADLINE..........(0x6E0) : 0x29A53848EDA

CPU Ratio Info:

------------------------------------

CPU Low Frequency Mode.............: 800 MHz

CPU Maximum non-Turbo Frequency....: 3300 MHz

CPU Maximum Turbo Frequency........: 3700 MHz

CPU P-States [ (8) 31 36 ]

CPU C3-Cores [ 0 1 ]

CPU C6-Cores [ 0 1 3 ]

CPU C7-Cores [ 0 1 3 ]

CPU P-States [ 8 31 33 36 (37) ]

CPU C3-Cores [ 0 1 2 3 ]

CPU P-States [ (8) 25 31 33 36 37 ]

CPU P-States [ 8 25 29 31 33 36 (37) ]

CPU P-States [ (8) 24 25 29 31 33 36 37 ]

CPU P-States [ 8 24 25 27 29 31 33 (35) 36 37 ]

CPU C7-Cores [ 0 1 2 3 ]

CPU P-States [ (8) 17 24 25 27 29 31 33 35 36 37 ]

CPU P-States [ 8 17 24 25 27 28 29 31 (33) 35 36 37 ]

CPU P-States [ (8) 17 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 17 18 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 17 18 22 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 15 17 18 22 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 15 16 17 18 22 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 15 16 17 18 21 22 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 15 16 17 18 20 21 22 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 14 15 16 17 18 20 21 22 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 14 15 16 17 18 19 20 21 22 24 25 26 27 28 29 31 33 35 36 37 ]

CPU P-States [ (8) 14 15 16 17 18 19 20 21 22 24 25 26 27 28 29 30 31 33 35 36 37 ]

CPU P-States [ (8) 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 33 35 36 37 ]

CPU P-States [ 8 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 35 (36) 37 ]

CPU P-States [ (8) 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 35 36 37 ]

CPU C6-Cores [ 0 1 2 3 ]

CPU P-States [ 8 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 (33) 34 35 36 37 ]

CPU P-States [ (8) 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 ]

CPU P-States [ (8) 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 ]Edhawk

Moderator

- Joined

- Aug 2, 2013

- Messages

- 6,324

- Motherboard

- Asus ROG Strix X570-F Gaming

- CPU

- Ryzen 9 3900X

- Graphics

- RX 6700 XT

- Mac

- Mobile Phone

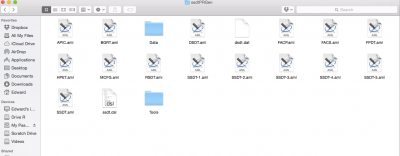

The generate process also dumps a number of other .aml files in the ~/Library/ssdtPRGen/ folder should we be using any of these?

I have ssdt.aml through to ssdt-5.aml in the folder, they do not appear to contain the same information.

The files were generated on my main hack with GA-Z97X-UD5H-BK, i7 4790K I had similar files generated when sorting out PM on my other machine.

I have ssdt.aml through to ssdt-5.aml in the folder, they do not appear to contain the same information.

The files were generated on my main hack with GA-Z97X-UD5H-BK, i7 4790K I had similar files generated when sorting out PM on my other machine.

Attachments

RehabMan

Moderator

- Joined

- May 2, 2012

- Messages

- 181,058

- Motherboard

- Intel DH67BL

- CPU

- i7-2600K

- Graphics

- HD 3000

- Mac

- Mobile Phone

The generate process also dumps a number of other .aml files in the ~/Library/ssdtPRGen/ folder should we be using any of these?

No. They are just side effects of the script.

Copyright © 2010 - 2024 tonymacx86 LLC