- Joined

- Oct 6, 2018

- Messages

- 100

- Motherboard

- Elite X2 1012 G2 << need manufacturer >> See Forum Rules !!

- CPU

- i5-7300U

- Graphics

- HD 620, 2736 x 1824

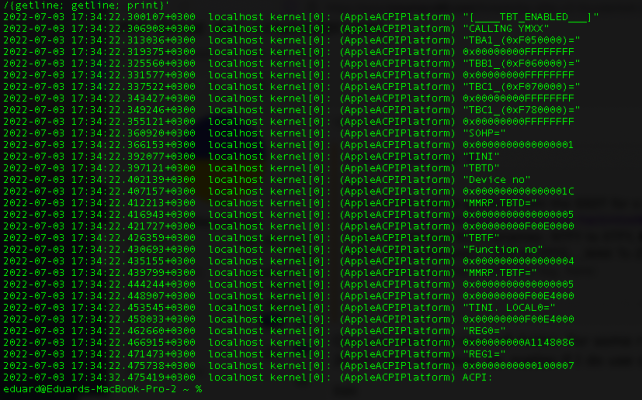

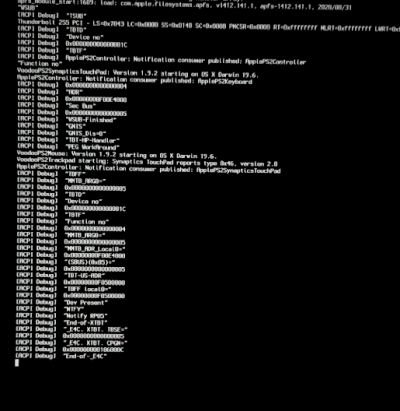

Different devices have different values assigned to REG6 at TINI. I have no idea why though.

Intel Kabylake Platforms https://github.com/tianocore/edk2-p...oardPkg/Features/Tbt/AcpiTables/Tbt.asl#L1110 0xF0F000

X1C6 https://raw.githubusercontent.com/t...in/ACPI/Disassembled ACPI/BIOS-v1.51/DSDT.dsl assigned with its own value at the end

Z370 AORUS GAMING 7 https://github.com/korzhyk/CLOVER-Z...0 AORUS Gaming 7/ACPI/patched/DSDT.dsl#L16001 not assigned anything

LG Gram 13Z980 https://raw.githubusercontent.com/suzuke/LG-Gram-13z980-Opencore/master/ACPI_Origin/DSDT.dsl 0xF0F000

And reading from https://osy.gitbook.io/hac-mini-guide/details/thunderbolt-3-fix-part-2 I think it has to do with force power and making PID visible to OS.

Intel Kabylake Platforms https://github.com/tianocore/edk2-p...oardPkg/Features/Tbt/AcpiTables/Tbt.asl#L1110 0xF0F000

X1C6 https://raw.githubusercontent.com/t...in/ACPI/Disassembled ACPI/BIOS-v1.51/DSDT.dsl assigned with its own value at the end

Z370 AORUS GAMING 7 https://github.com/korzhyk/CLOVER-Z...0 AORUS Gaming 7/ACPI/patched/DSDT.dsl#L16001 not assigned anything

LG Gram 13Z980 https://raw.githubusercontent.com/suzuke/LG-Gram-13z980-Opencore/master/ACPI_Origin/DSDT.dsl 0xF0F000

And reading from https://osy.gitbook.io/hac-mini-guide/details/thunderbolt-3-fix-part-2 I think it has to do with force power and making PID visible to OS.

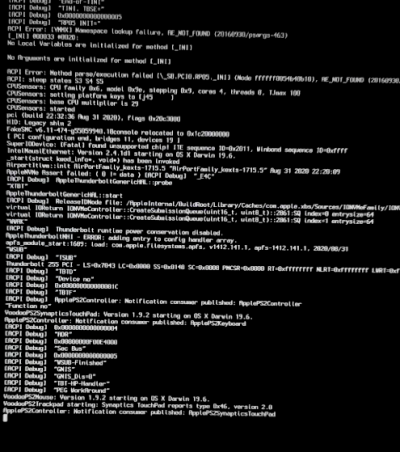

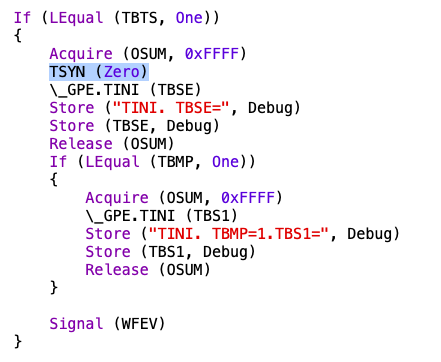

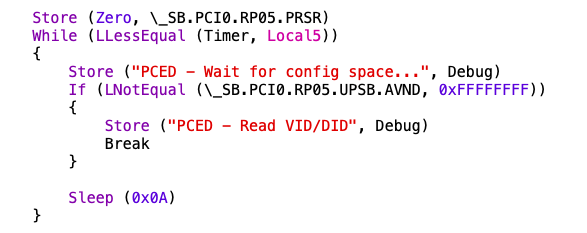

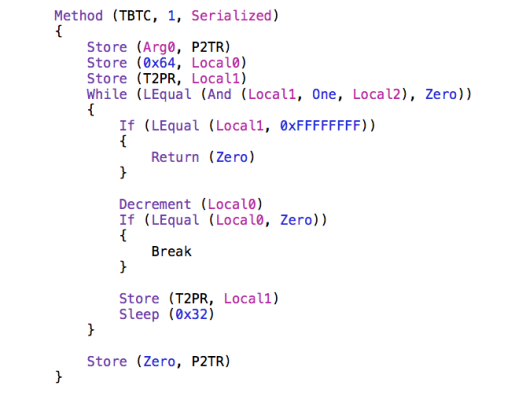

OSUP is called in TINI right after REG6 is given a hardcoded value.If powered on with the force power GPIO, the Ridge will identify itself with a PID of 0xFFFFFFFF. This is because most code that detects if a PCI device exists will read the PID register and check that it is NOT 0xFFFFFFFF. Effectively, the Ridge is cloaking itself when it is powered on without any devices attached. I can only speculate that it is for some weird compatibility reasons. For the PID to show up properly, the CPU uses a pair of undocumented registers in the PCI configuration space at offset 0x54C. It writes 0xD to register 0x54C and then polls 0x548 until bit 0 is set. According to the openboard UEFI source, these are mailbox registers for communicating with the Ridge host controller. The NUC's ACPI code will do this handshake automatically on init through a method called OSUP. This OSUP command seems to be a way for the CPU to indicate to the Ridge that it is out of BIOS/DXE mode and is in the OS proper and therefore is safe for it to come out and declare its PID to the world.