- Joined

- May 18, 2014

- Messages

- 202

- Motherboard

- ASUS S500CA LAPTOP

- CPU

- Intel Core i5-3317U @ 1.70GHz

- Graphics

- INTEL HD 4000

- Mac

- Classic Mac

- Mobile Phone

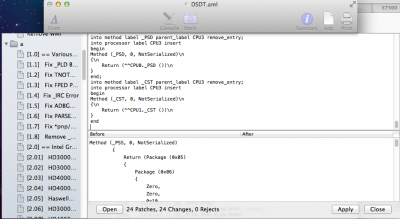

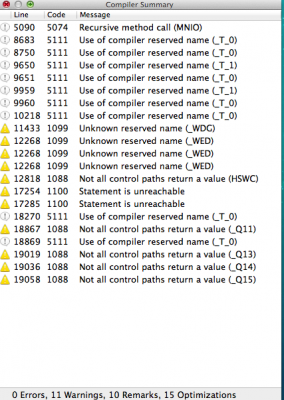

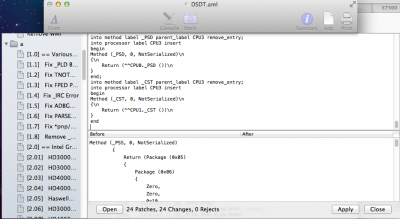

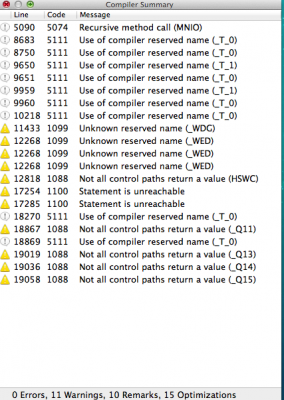

So , i find on the google , some speedstep DSDT patches.

and a lots got me on error at compile.

but here is the bomb.

and yeah , i still have hi temperature on CPU.

some intel staff say is ok, some assus staff is is not.

i don't know what to believe.

Intel® Core™2 Duo Processor E7300 speedstep is working without any error , when i compile.

is this good, i should use it , or .. no.?

*progress.

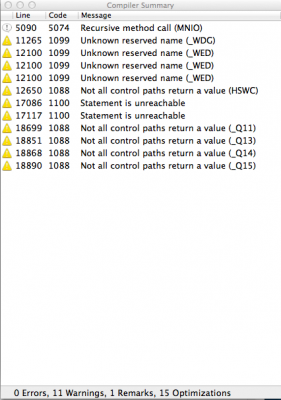

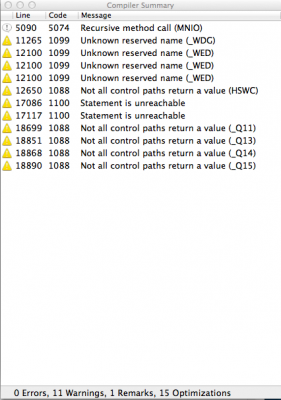

9 remarks disapear. haha

Can someone illuminate me ?

If the patch work .. is good to use ?

because , I'm so confuse right now..

theess patchess.

and a lots got me on error at compile.

but here is the bomb.

and yeah , i still have hi temperature on CPU.

some intel staff say is ok, some assus staff is is not.

i don't know what to believe.

Intel® Core™2 Duo Processor E7300 speedstep is working without any error , when i compile.

is this good, i should use it , or .. no.?

Code:

# Insert methods _PSS (for E7300), _PSD and _CST into CPUs 0-3#

into method label _PSS parent_label CPU0 remove_entry;

into processor label CPU0 insert

begin

Method (_PSS, 0, NotSerialized)\n

{\n

Return (Package (0x05)\n

{\n

Package (0x06)\n

{\n

Zero, \n

Zero, \n

0x10, \n

0x10, \n

0x0A20, // FF = FID, VV = VID\n

Zero // P-state 0\n

}, \n

Package (0x06)\n

{\n

Zero, \n

Zero, \n

0x10, \n

0x10, \n

0x091F, // FF = FID, VV = VID\n

One // P-state 1\n

}, \n

Package (0x06)\n

{\n

Zero, \n

Zero, \n

0x10, \n

0x10, \n

0x081D, // FF = FID, VV = VID\n

0x02 // P-state 2\n

}, \n

Package (0x06)\n

{\n

Zero, \n

Zero, \n

0x10, \n

0x10, \n

0x071C, // FF = FID, VV = VID\n

0x03 // P-state 3\n

}, \n

Package (0x06)\n

{\n

Zero, \n

Zero, \n

0x10, \n

0x10, \n

0x061A, // FF = FID, VV = VID\n

0x04 // P-state 4\n

}\n

})\n

}

end;

into method label _PSD parent_label CPU0 remove_entry;

into processor label CPU0 insert

begin

Method (_PSD, 0, NotSerialized)\n

{\n

Return (Package (0x05)\n

{\n

0x05, \n

Zero, \n

Zero, \n

0xFC, \n

0x02\n

})\n

}

end;

into method label _CST parent_label CPU0 remove_entry;

into processor label CPU0 insert

begin

Method (_CST, 0, NotSerialized)\n

{\n

Return (Package (0x02)\n

{\n

One, \n

Package (0x04)\n

{\n

ResourceTemplate ()\n

{\n

Register (FFixedHW, \n

0x01, // Bit Width\n

0x02, // Bit Offset\n

0x0000000000000000, // Address\n

0x01, // Access Size\n

)\n

}, \n

One, \n

0x9D, \n

0x03E8\n

}\n

})\n

}

end;

into method label _PSS parent_label CPU1 remove_entry;

into processor label CPU1 insert

begin

Method (_PSS, 0, NotSerialized)\n

{\n

Return (^^CPU0._PSS ())\n

}

end;

into method label _PSD parent_label CPU1 remove_entry;

into processor label CPU1 insert

begin

Method (_PSD, 0, NotSerialized)\n

{\n

Return (^^CPU0._PSD ())\n

}

end;

into method label _CST parent_label CPU1 remove_entry;

into processor label CPU1 insert

begin

Method (_CST, 0, NotSerialized)\n

{\n

Return (Package (0x04)\n

{\n

0x03, \n

Package (0x04)\n

{\n

ResourceTemplate ()\n

{\n

Register (FFixedHW, \n

0x01, // Bit Width\n

0x02, // Bit Offset\n

0x0000000000000000, // Address\n

,)\n

}, \n

One, \n

Zero, \n

0x03E8\n

}, \n

Package (0x04)\n

{\n

ResourceTemplate ()\n

{\n

Register (FFixedHW, \n

0x08, // Bit Width\n

0x00, // Bit Offset\n

0x0000000000000414, // Address\n

,)\n

}, \n

0x02, \n

One, \n

0x01F4\n

}, \n

Package (0x04)\n

{\n

ResourceTemplate ()\n

{\n

Register (FFixedHW, \n

0x08, // Bit Width\n

0x00, // Bit Offset\n

0x0000000000000415, // Address\n

,)\n

}, \n

0x03, \n

0x55, \n

0xFA\n

}\n

})\n

}

end;

into method label _PSS parent_label CPU2 remove_entry;

into processor label CPU2 insert

begin

Method (_PSS, 0, NotSerialized)\n

{\n

Return (^^CPU0._PSS ())\n

}

end;

into method label _PSD parent_label CPU2 remove_entry;

into processor label CPU2 insert

begin

Method (_PSD, 0, NotSerialized)\n

{\n

Return (^^CPU0._PSD ())\n

}

end;

into method label _CST parent_label CPU2 remove_entry;

into processor label CPU2 insert

begin

Method (_CST, 0, NotSerialized)\n

{\n

Return (^^CPU1._CST ())\n

}

end;

into method label _PSS parent_label CPU3 remove_entry;

into processor label CPU3 insert

begin

Method (_PSS, 0, NotSerialized)\n

{\n

Return (^^CPU0._PSS ())\n

}

end;

into method label _PSD parent_label CPU3 remove_entry;

into processor label CPU3 insert

begin

Method (_PSD, 0, NotSerialized)\n

{\n

Return (^^CPU0._PSD ())\n

}

end;

into method label _CST parent_label CPU3 remove_entry;

into processor label CPU3 insert

begin

Method (_CST, 0, NotSerialized)\n

{\n

Return (^^CPU1._CST ())\n

}

end

*progress.

Code:

into_all all code_regex _T_0 replaceall_matched begin T_0 end;into_all all code_regex _T_1 replaceall_matched begin T_1 end;

into_all all code_regex _T_2 replaceall_matched begin T_2 end;

into_all all code_regex _T_3 replaceall_matched begin T_3 end;

into_all all code_regex _T_4 replaceall_matched begin T_4 end;

into_all all code_regex _T_5 replaceall_matched begin T_5 end;

into_all all code_regex _T_6 replaceall_matched begin T_6 end

9 remarks disapear. haha

Can someone illuminate me ?

If the patch work .. is good to use ?

because , I'm so confuse right now..

theess patchess.