Just a return of my recent iterations with Thunderbolt on X299 with the way that I mentioned in my previous post.

At the end of 2018 some users stated that it was impossible to get the Thunderbolt device tree materialised.

But actually it is real on Z390 Designare Mobo and the good point without bios tweak.

But on X299 Mobo, the approach between Pch and Pci must be adapted.

Unlike before when we tried with Kgp and @

nmano to adopt iMac Pro TB SSDT9 during sumer 2018 (on this thread

#101 ) there are not so many errors at startup in vebose

- the SSDT load :

Code:

37:843 0:000 Inserting SSDT-TbtPch-X299 Draft07-Fix-USBC.aml from EFI\CLOVER\ACPI\patched: size=21887 ... Success

But some problems remain:

- Thunderbolt device tree just partially materialised and NO Thunderbolt bus.

- Errors on Method Parse/Execution while booting return here on SSDT :

Code:

Method (UGIO, 0, Serialized)

{

Acquire (TCFG, 0xFFFF)

If (LEqual (\_SB.PCI0.RP17.GPCI, Zero))

Code:

Method (PCDA, 0, Serialized)

{

DBG1 ("PCDA DSB0")

If (LNotEqual (\_SB.PCI0.RP17.UPSB.DSB0.POFF (), Zero))

{

Store (Zero, \_SB.PCI0.RP17.UPSB.DSB0.PCIA)

DBG1 ("PCDA DSB0- Put upstream bridge into D3")

Store (0x03, \_SB.PCI0.RP17.UPSB.DSB0.PSTA)

DBG1 ("PCDA DSB0- Set link disable on upstream bridge")

Store (One, \_SB.PCI0.RP17.UPSB.DSB0.LDIS)

DBG1 ("PCDA DSB0- Wait for link to drop...")

Add (Timer, 0x00989680, Local5)

While (LLessEqual (Timer, Local5))

{

Code:

Method (_PS3, 0, Serialized) // _PS3: Power State 3

{

DBG1 ("_PS3 DSB0")

PCDA ()

}

- My approach is different to inject Thunderbolt properties, while my attempt is to inject with SSDT their success method is to inject with Clover in the config.plist and the values are for GC Titan Ridge :

Code:

<key>PciRoot(0x0)/Pci(0x1c,0x4)/Pci(0x0,0x0)/Pci(0x0,0x0)/Pci(0x0,0x0)</key>

<dict>

<key>TBTDPLowToHigh</key>

<data>AQAAAA==</data>

<key>TBTFlags</key>

<data>AwAAAA==</data>

<key>ThunderboltConfig</key>

<data>AAL//wQAAwEBAAQABQECAAMAAwEBAAAAAwECAAIAAQA=</data>

<key>ThunderboltDROM</key>

<data>cQAAAAAAAO0A4EA0mAFpAO0ACMABAQiBgAKAAAAACIKQAYAAAAAIg4AEgAEAAAiEkAOAAQAABYVQAAAFhlAAAALHC4ggAQBkAAAAAAADiYAFilBAAAWLUEAACwFHSUdBQllURQARAlozOTAgREVTSUdOQVJFAA==</data>

<key>linkDetails</key>

<data>CAAAAAMAAAA=</data>

<key>pathcr</key>

<data>BAAAAAAAAAAAAAcAEAAQAAUAAAAAAAAAAAAHABAAEAABAAAACwAOAA4AAAAAAAAAAgAAAAAAAAAAAAQAAgABAAMAAAAAAAAAAAAHAAIAAQA=</data>

</dict>

But there are some progress .

Why I asked for help and at this point I am not an alien (E.T. : humour on ):

I think the goal is not as far and nearer than ever, but trying and developing takes time and patience.

What we need to achieve : some users ( volunteers) , a reserved MacOs Mojave or Catalina on a SSD not our main system ( but it does not matter for me...)

And a little time to do some test.

For now I will try to have the same approach by injecting Thunderbolt properties with Clover in config.plist so just to change the lignes on Method (_DSM, under NHI0, ( and also but seems to be normal in fact : why I got invalid reg Data on UPSB and DBS0).

EDIT :

Tracing back to Kgp guide :

It is recommended for Prime Deluxe to put the Thunderbolt on PCIE16_3 slot :

And than we should add on the SSDT / GPE :

Code:

Method (_L69, 0, NotSerialized) // _Lxx: Level-Triggered GPE

{

\RMDT.P1 ("_L69 Tbt")

Notify (\_SB.PC01.BR1A.UPSB.AMPE ()

Notify (\_SB.PC01.BR1A.PEGP.UPSB.UMPE ()

GPE is actually missing on my SSDT.

So i will try to change my PCie add in card location if no more progress with the actual.

EDIT 2 :

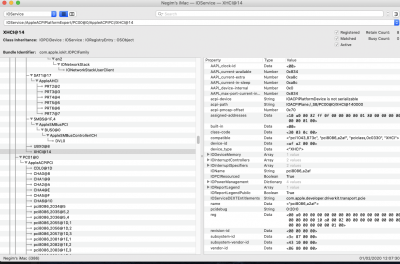

Intel DSL6540 Thunderbolt Controller Alpine Ridge :

Code:

ThunderboltDROM

<76 00 c1 71 c5 be 49 01 00 0a 9b 60 fa 01 5e 00 01 00 0c 00 01 00 08 81 80 02 80 00 00 00 08 82 90 01 80 00 00 00 08 83 80 04 80 01 00 00 08 84 90 03 80 01 00 00 08 85 00 00 00 00 00 00 03 86 20 03 87 80 02 c8 05 89 50 00 00 05 8a 50 00 00 02 cb 0d 01 41 70 70 6c 65 20 49 6e 63 2e 00 0c 02 4d 61 63 69 6e 74 6f 73 68 00>

dgDBccW+SQEACptg+gFeAAEADAABAAiBgAKAAAAACIKQAYAAAAAIg4AEgAEAAAiEkAOAAQAACIUAAAAAAAADhiADh4ACyAWJUAAABYpQAAACyw0BQXBwbGUgSW5jLgAMAk1hY2ludG9zaAA=

pathcr

<04 00 00 00 00 00 00 00 00 00 07 00 10 00 10 00 05 00 00 00 00 00 00 00 00 00 07 00 10 00 10 00 01 00 00 00 0b 00 0e 00 0e 00 00 00 00 00 00 00 02 00 00 00 00 00 00 00 00 00 04 00 02 00 01 00 03 00 00 00 00 00 00 00 00 00 07 00 02 00 01 00>

BAAAAAAAAAAAAAcAEAAQAAUAAAAAAAAAAAAHABAAEAABAAAACwAOAA4AAAAAAAAAAgAAAAAAAAAAAAQAAgABAAMAAAAAAAAAAAAHAAIAAQA=

ThunderboltConfig

<00 02 ff ff 04 00 03 01 01 00 04 00 05 01 02 00 03 00 03 01 01 00 00 00 03 01 02 00 02 00 01 00>

AAL//wQAAwEBAAQABQECAAMAAwEBAAAAAwECAAIAAQA=