- Joined

- Sep 8, 2011

- Messages

- 77

- Motherboard

- Asus WS X299 SAGE 10G

- CPU

- i9-7960X

- Graphics

- WX4100

- Mac

- Mobile Phone

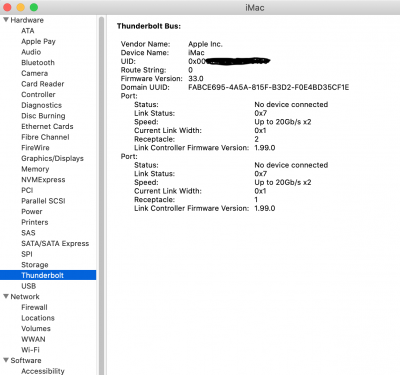

Same... I had a DTPG with Device (RMDT) [for test purpose]. I tried original DTPG instead of.Please copy both of the attached SSDTs to CLOVER/ACPI/patched. Reboot and check IORegistry again.

I can't load thunderbolt properties with aml for BR3B.