CaseySJ

Moderator

- Joined

- Nov 11, 2018

- Messages

- 22,177

- Motherboard

- Asus ProArt Z690-Creator

- CPU

- i7-12700K

- Graphics

- RX 6800 XT

- Mac

- Classic Mac

- Mobile Phone

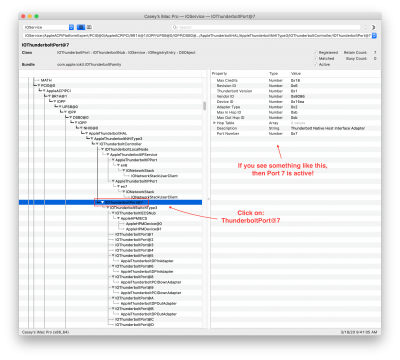

On my X99 Deluxe II with flashed GC-Titan Ridge, no problem seeing IOThunderboltFamily. I'll create the Thunderbolt DROM Modification Mini-Guide, but if anyone runs into this problem -- you're on your own until we can figure this out!Your log is similar to the other two, but you have 2 additional IOThunderboltFamily entries. I will check this on my other system:

- Asus X99 Deluxe II with flashed GC-Titan Ridge. Will see if IOThunderboltFamily appears there.

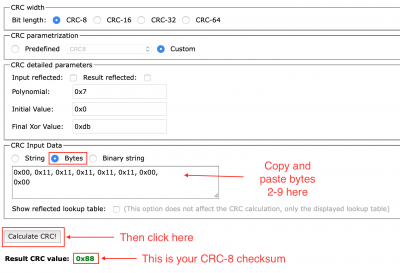

@maleorderbride : I'm still quite interested in finding a solution. Did you enable Port 7 by updating the firmware? If you need a valid CRC32_C generated for your DROM, just send me a private message with the DROM.

kernel: (AppleThunderboltNHI) AppleThunderboltGenericHAL: Probe

kernel: (AppleThunderboltNHI) 7195944us AppleThunderboltGenericHAL: Probe

kernel: (AppleThunderboltNHI) AppleThunderboltGenericHAL::start

kernel: (AppleThunderboltNHI) 7195978us AppleThunderboltGenericHAL::start

kernel: (AppleThunderboltNHI) Thunderbolt runtime power conservation disabled.

kernel: (AppleThunderboltNHI) Thunderbolt runtime power conservation disabled.

kernel: (AppleThunderboltNHI) AppleThunderboltNHI - ERROR: adding entry to config handler array.

kernel: (AppleThunderboltNHI) 7196414us AppleThunderboltNHI - ERROR: adding entry to config handler array.

kernel: (AppleThunderboltNHI) Thunderbolt 255 PCI - LS=0xf043 LC=0x0040 SS=0x0040 SC=0x07cb PMCSR=0x0008 RT=0xffffffff NLRT=0xffffffff LWRT=0xffffffff PRRT=0xffffffff TRT=0x0000 TNLRT=0x0000 TLWRT=0x0000 TPRRT=0x0000 TLUP=0x0001

kernel: (AppleThunderboltNHI) Thunderbolt 255 PCI - LS=0xf043 LC=0x0040 SS=0x0040 SC=0x07cb PMCSR=0x0008 RT=0xffffffff NLRT=0xffffffff LWRT=0xffffffff PRRT=0xffffffff TRT=0x0000 TNLRT=0x0000 TLWRT=0x0000 TPRRT=0x0000 TLUP=0x0001

kernel: (IOThunderboltFamily) IOThunderboltSwitch<0x0>(0x0)::listenerCallback - Thunderbolt HPD packet for route = 0x0 port = 5 unplug = 0

kernel: (IOThunderboltFamily) IOThunderboltSwitch<0x0>(0x0)::listenerCallback - Thunderbolt HPD packet for route = 0x0 port = 6 unplug = 0

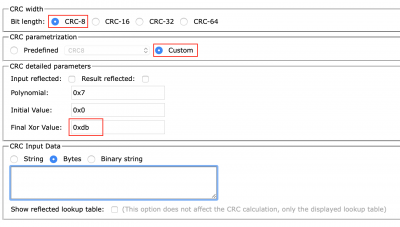

kernel: (IOThunderboltFamily) IOThunderboltEEPROM:: parseDROMData - Failed CRC8 Verification: 0x10 != 0x2b

kernel: (IOThunderboltFamily) IOThunderboltEEPROM::getDROM - Error getting DROM from I/O Registry (0xe0000001)

fud: (MobileAccessoryUpdater) Stream event happened for filter: com.apple.MobileAsset.MobileAccessoryUpdate.ThunderboltType3Switch

fud: (MobileAccessoryUpdater) -[FudStateMachine isActive]: state=6 nextState=-1 filter=com.apple.MobileAsset.MobileAccessoryUpdate.ThunderboltType3Switch