CaseySJ

Moderator

- Joined

- Nov 11, 2018

- Messages

- 22,195

- Motherboard

- Asus ProArt Z690-Creator

- CPU

- i7-12700K

- Graphics

- RX 6800 XT

- Mac

- Classic Mac

- Mobile Phone

Just FYI...last night I modified TbtOnPch as follows:

- Only a simplified Ssdt TbtonPCH (without preconfiguration methods ICMS/CNHI and stay with boot register values for RP18,...NH10

- I had this 0xE00002eb error before firmware modification resulting on self disconnecting after around 20s. Now it is not prefect, i dont have 0x101 for normal results but always 0x7 with no device connected and 0x2 when connected. I suppose that is related to XHC2 not visible at boot or something else

- I will send u my current SSDT and modified firmware if you want to post it ( it include DROM from iMac19,1).. We still have to understand CRC32/CRC8 on TbtDROM to custom each firmware ( UUID and if we want the device name)

- Created method to display Link Status of all 4 ports. Why 4 ports? Because that's what latest Linux kernel does. The ports are numbered 1, 2, 3, 4.

- Connected only one TB3 device at a time.

- This SSDT sets P2TR mailbox register to 0x05.

- Hot plug does not work.

- Test 1: Connect TB device to top port.

- Result:

- Port 1: 0x02 Device Connected (top port)

- Port 2: 0x07 No device connected

- Port 3: 0x07 No device connected

- Port 4: 0x07 No device connected

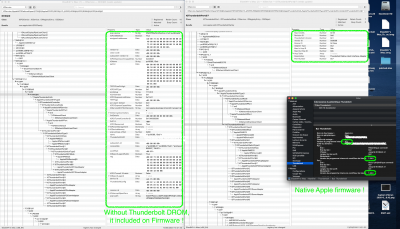

- In IOReg, we see device connected to DSB1.

- Result:

- Test 2: Connect TB device to bottom port.

- Resut:

- Port 1: 0x07 No device connected

- Port 2: 0x07 No device connected

- Port 3: 0x02 Device Connected (bottom port)

- Port 4: 0x07 No device connected

- In IOReg, we see device connected to DSB1. (It still shows up under DSB1 instead of DSB4.)

- Resut:

- The first physical port gets logical port numbers 1 and 2.

- The second port gets logical port numbers 3 and 4.

- Even though the device is properly detected on the right port, it attaches only to DSB1 regardless of the physical port.

- Hotplug works.

- TNODE/TBUS do not always show up, but they will show up under some circumstances.

- Port link state is the same as before:

- Logical ports 1 and 2 belong to Physical Port 1.

- Logical ports 3 and 4 belong to Physical Port 2.

- And IOReg is correct:

- TB3 device in Port 1 --> attaches to DSB1.

- TB3 device in Port 2 --> attaches to DSB4.

Based on this, I decided to check something else:

- I switched back to P2TR = 0x05 so that TNODE/TBUS will always appear.

- After ICMS(), I reset all 4 logical ports (because Linux kernel also does this) by issuing special commands to CRMW(). The commands are:

- Disable all ports first:

- CRMW (0x37, 1, 1, 0x00004000, 0x00004000) // disable port 1

- CRMW (0x37, 2, 1, 0x00004000, 0x00004000) // disable port 2

- CRMW (0x37, 3, 1, 0x00004000, 0x00004000) // disable port 3

- CRMW (0x37, 4, 1, 0x00004000, 0x00004000) // disable port 4

- Re-enable all ports:

CRMW (0x37, 1, 1, 0x00004000, 0x00000000) // enable port 1CRMW (0x37, 2, 1, 0x00004000, 0x00000000) // enable port 2CRMW (0x37, 3, 1, 0x00004000, 0x00000000) // enable port 3CRMW (0x37, 4, 1, 0x00004000, 0x00000000) // enable port 4- CRMW (0x37, 1, 1, 0x00000000, 0x00004000) // enable port 1

- CRMW (0x37, 2, 1, 0x00000000, 0x00004000) // enable port 2

- CRMW (0x37, 3, 1, 0x00000000, 0x00004000) // enable port 3

- CRMW (0x37, 4, 1, 0x00000000, 0x00004000) // enable port 4

- Disable all ports first:

- Result:

Link State for both Receptacle 1 and Receptacle 2 in System Information --> Thunderbolt changes:From:0xe00002eb

To:0x101

- Update 14 Mar 2020: Link State remains the same after resetting ports (0xe00002eb).

- But no devices attach to the ports. Any device that was previously attached during boot gets disconnected.

- I think this is due to some (small) problem with CTBT() or NHI0.PCED().

Last edited: